N-type Organic Thin Film Transistors (OTFT): Effects of treatments of the insulator/semiconductor interface on the devices performances

Maria Rosa Fiorillo

### FONDO SOCIALE EUROPEO Programma Operativo Nazionale 2000/2006 "Ricerca Scientifica, Sviluppo Tecnologico, Alta Formazione" Regioni dell'Obiettivo 1 – Misura III.4 "Formazione superiore ed universitaria"

### Department of Industrial Engineering

Ph.D. Course in Industrial Engineering (XV Cycle-New Series, XXIX Cycle)

### N-type Organic Thin Film Transistors (OTFT): Effects of treatments of the insulator/semiconductor interface on the devices performances

Supervisors Prof. Alfredo Rubino Tutor ENEA Ing. Paolo Tassini **Ph.D. Student** *Maria Rosa Fiorillo*

Scientific Referees Prof. Francesco Della Corte Dr. Luigi Mariucci

**Ph.D. Course Coordinator** *Prof. Ernesto Reverchon*

To my husband

### List of works

### Journal papers

*Electrical model for admittance spectroscopy in n-type thin film transistors* M. R. Fiorillo, R. Liguori, C. Diletto, P.Tassini, M. G. Maglione, P. Maddalena, C. Minarini, A. Rubino, in preparation

Influence of the fabrication processes on the gate bias-stress effects in TIPSpentacene OTFTs

R. Rega, P. Tassini, A. De Girolamo Del Mauro, G. Pandolfi, E. Calò, T. Fasolino, M. R. Fiorillo, A. Negrier, R. Miscioscia, M. G. Maglione, C. Minarini, P. Maddalena, H. L. Gomes, in preparation

### **Conference proceedings**

Trap Density Analysis in PC<sub>70</sub>BM n-type Thin Film Transistors through Admittance Studies

M. R. Fiorillo, R. Liguori, C. Diletto, E. Bezzeccheri, P.Tassini, M. G. Maglione, P. Maddalena, C. Minarini, A. Rubino, Materials Today: Proceedings 4, Salonicco, submitted

$PC_{70}BM$  n-type thin film transistors: Influence of HMDS deposition temperature on the devices properties

M. R. Fiorillo, C. Diletto, P. Tassini, M. G. Maglione, E. Santoro, F. Villani, R. Liguori, P. Maddalena, A. Rubino, C. Minarini, Materials Today: Proceedings 3, 720-726, Salonicco, December 2016

Evaluation of the stability of different encapsulated blue oleds E. Santoro, S. Aprano, G. Sico, M. R. Fiorillo, M.G. Maglione, P. Tassini,

A. Rubino, C. Minarini, IET Conference Publications, Torino, Maggio 2015

### Poster

SINFO 2016 - Methods for studying and improving performance of organic electronic devices

S. Aprano, E. Bezzeccheri, M. R. Fiorillo, R. Liguori, E. Santoro, A. Rubino, C. Diletto, M. G. Maglione, G. Sico, P. Tassini, C. Minarini, Napoli, Giugno 2016

EOS'15 - Fabrication and characterization of a blue OLED based on  $\alpha$ -NPD as emitting-layer

S. Aprano, E. Santoro, M. Tesoro, C. T. Prontera, C. Diletto, M. R. Fiorillo, G. Cuomo, V. Criscuolo, P. Manini, A. Pezzella, G. Sico, M. G. Maglione, P. Tassini, A. Rubino, C. Minarini, Capri, Settembre 2015

GE Conference 2015 - *Study and fabrication of selected organic electronic devices to improve performance and stability*

S. Aprano, E. , Bezzeccheri, M. R. Fiorillo, R. Liguori, E. Santoro, A. Rubino, C. Diletto, M. G. Maglione, G. Sico, P. Tassini, C. Minarini, Siena, Giugno 2015

Nanotech Italy 2013 - Development of phosphorescent OLEDs for general lighting applications

M. G. Maglione, S. Aprano, P. Tassini, M.R. Fiorillo, E. Santoro, V. Criscuolo, P. Manini, A. De Girolamo Del Mauro, R. Rega, G. Pandolfi and C. Minarini, Venezia, Novembre 2013

# Contents

| Contents                                                                | I     |

|-------------------------------------------------------------------------|-------|

| List of Figures                                                         | III   |

| List of Tables                                                          |       |

| Abstract                                                                | XI    |

| Introduction                                                            |       |

|                                                                         |       |

| Chapter I Organic Semiconductors                                        |       |

| I.1. Physics of Organic Semiconductors                                  |       |

| I.2. Charge transport mechanisms                                        |       |

| I.3. Charge carrier injection                                           |       |

| I.4. Defects in organic semiconductors                                  |       |

| I.5. Organic electronics today and tomorrow                             | 13    |

| Chapter II Organic Thin Film Transistors                                | 17    |

| II.1. Thin-film Transistor fundamentals                                 |       |

| II.2. Architectures                                                     |       |

| II.3. Materials                                                         |       |

| II.4. Operation Principle of OTFTs                                      |       |

| II.4.1. Transistor Parameters                                           |       |

| II.4.2. Non- ideal transistor behavior                                  |       |

| II.5. Traps in OTFTs                                                    |       |

| II.6. Evolution of the OTFTs                                            |       |

| Chapter III Fabrication of OTFTs                                        | 27    |

| III.1. Architecture of the devices                                      |       |

|                                                                         |       |

| III.2. Fabrication of the OTFTs                                         |       |

| III.3. Cleaning of the SiO <sub>2</sub> surface with $UV/O_3$ treatment |       |

| III.4. Surface Treatments of Self-Assembled Monolayer (SAM)             |       |

| III.4.1. Temperature dependence of the SAM formation                    |       |

| III.4.2. Time dependence of the SAM formation                           |       |

| III.5. Source and Drain Electrodes in OTFTs                             |       |

| III.6. Growth of Organic Semiconductor                                  | 49    |

| Chapter IV Materials preparation and characterization and OTFT          | Гs DC |

| analysis                                                                |       |

| IV.1. Analysis of HMDS Treatments                                       | 53    |

| IV.1.1. Results of the experimental step                                |       |

| IV.2. Morphology Analysis of the deposited Organic Semiconductor        |       |

| IV.2.1. Results of the experimental step                                |       |

| IV.3. DC Measurement                                                    |       |

|                                                                         |       |

| IV.3.1. Results of the experimental step                                   | 61       |

|----------------------------------------------------------------------------|----------|

| IV.4. Discussion of the data - Comparing the electrical parameters vs. the | <u>)</u> |

| hydrophobic characteristics                                                | 64       |

|                                                                            |          |

| Chapter V Equivalent Circuit AC Model                                      | 67       |

| V.1. AC Measurement                                                        | 68       |

| V.1.1. Results of the experimental step                                    | 69       |

| V.2. Interface Characterization Technique                                  | 74       |

| V.3. Equivalent electrical model                                           | 76       |

| V.4. Models of the Bulk Traps Admittance                                   |          |

| V.4.1. Single trap level - Data Fitting                                    | 79       |

| V.4.1.1. Experimental data fitting and extracted parameters                |          |

| V.4.2. Distribution of single trap levels- Data Fitting                    | 86       |

| V.4.2.1. Experimental data fitting and extracted parameters                |          |

| V.4.3. Comparison between the models of single-level traps and of          |          |

| distribution of single trap-levels                                         | 95       |

| V.4.4. Comparison of DC vs.AC parameters                                   |          |

|                                                                            |          |

| Conclusion                                                                 | 99       |

| Bibliography                                                               | 103      |

| List of Symbols                                                            | 109      |

# **List of Figures**

| <b>Figure 1</b> : Schematic representation of the formation of $\sigma$ and $\pi$ molecular |

|---------------------------------------------------------------------------------------------|

| orbitals from two carbon atoms with sp <sup>2</sup> hybridization                           |

| <b>Figure 2</b> : <i>Representation of the transport mechanism in solids with applied</i>   |

| electric field, (a) for band transport conduction and (b) for hopping between               |

| localized states                                                                            |

| <b>Figure 3</b> : Distribution of trap states in the band gap for a p-type organic          |

| semiconductor                                                                               |

| Figure 4: Hopping transport through the localized states in the Gaussian                    |

| disorder model (GDM)                                                                        |

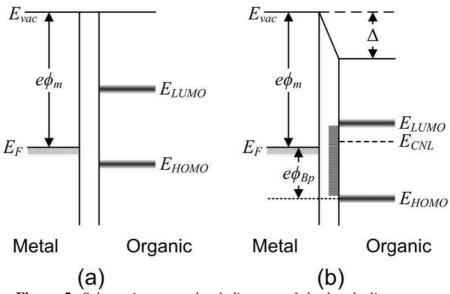

| Figure 5: Schematic energy level diagram of the band alignment at a metal                   |

| organic interface, (a) Mott-Schottky limit vacuum level alignment, and (b)                  |

| pinning of the Fermi level by induced interface states interfacial dipole 10                |

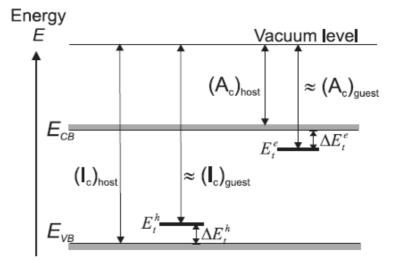

| Figure 6: Representation of the energy levels of a host material with                       |

| chemical impurities (Pope & Swenberg, 1999)12                                               |

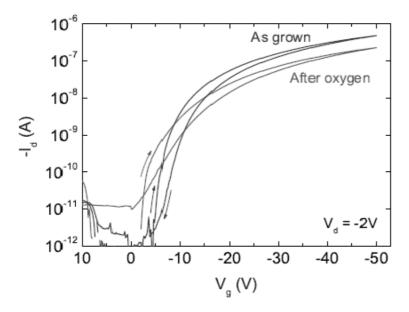

| Figure 7: Transfer characteristic of a pentacene transistor measured as                     |

| grown (blue line) and after oxidation (red line). The graph shows the                       |

| forward and the reverse sweeps in both cases                                                |

| Figure 8: Organic and printed electronics applications 6th edition of the                   |

| <i>OE-A roadmap</i> (2015)14                                                                |

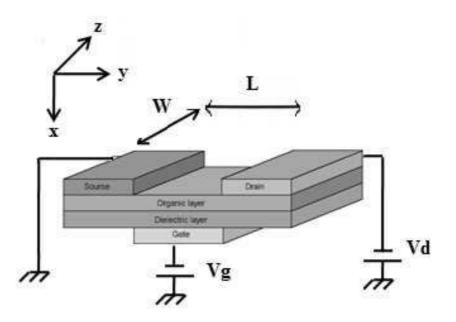

| Figure 9: Layer structure of an organic thin film transistor                                |

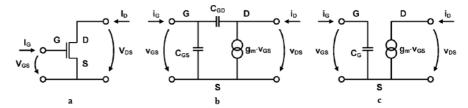

| <b>Figure10</b> : (a)Electrical symbol of a TFT, and (b and c) two small-signal             |

| equivalent circuits of a transistor, that show the gate-source capacitance                  |

| $C_{GS}$ , the gate-drain capacitance $C_{GD}$ , the equivalent gate capacitance $C_{G}$ ,  |

| and the current source $g_m v_{GS}$ (Klauk, 2010)                                           |

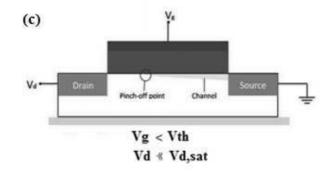

| <b>Figure 11</b> : Energy-level diagrams across the metal/dielectric/p-type                 |

| semiconductor interface of an organic transistor, showing (a)accumulation                   |

| mode, (b) flat-band mode, (c) depletion mode                                                |

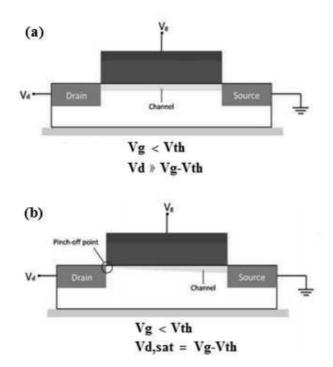

| <b>Figure 12</b> : Schematic operation regimes of p-type OTFT, (a) linear regime,           |

| (b) the start of saturation mode when the pinch-off point occurs, (c) the                   |

| saturation regime                                                                           |

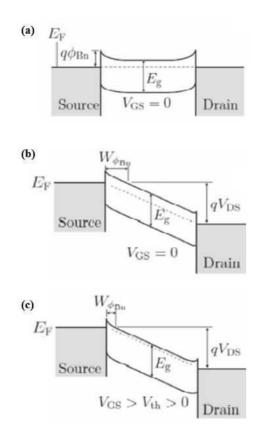

| <b>Figure 13</b> : Band diagram of the Schottky contacts to an n-type                       |

| semiconductor with metal contacts: (a) without applied voltages, (b) with                   |

| drain voltage only, and (c) with drain and gate voltages                                    |

|                                                                                             |

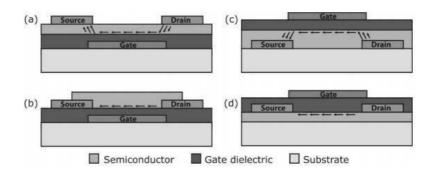

| С       | <b>igure 14</b> :General OTFT configurations: (a) staggered and bottom-gate ontact; (b) coplanar and bottom-gate bottom -contact; (c) staggered and                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

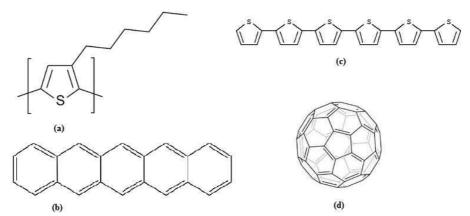

| F<br>ai | op-gate bottom-contact and (d) coplanar and top-gate top-contact<br>igure 15: Representation of a polymer: poly(3-hexylthiophene) (P3HT)<br>and of conjugated small-molecule organic semiconductors: pentacene (b) |

|         | exithiophene (6T) (c), fullerene ( $C_{60}$ ) (d)                                                                                                                                                                  |

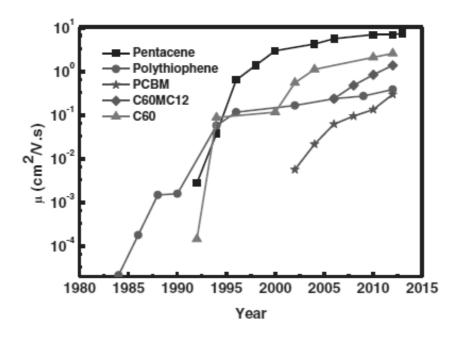

|         | <b>igure 16</b> : <i>Trend vs. time of mobility for some p-type (Pentacene and</i>                                                                                                                                 |

|         | olythiophene) and n-type organic semiconductors (Kumar et al., 2014).                                                                                                                                              |

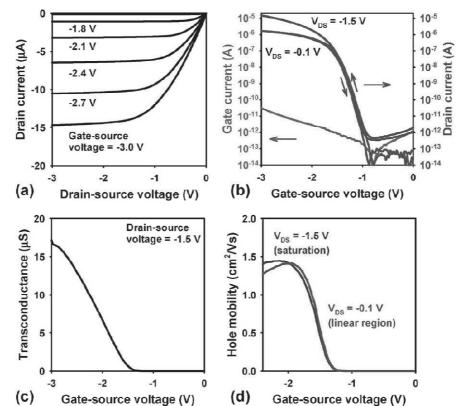

|         | igure 17: Typical electrical characteristics of an organic p-channel TF                                                                                                                                            |

|         | utput characteristics (a), input characteristics ( $I_g$ versus $V_g$ ) and transfer                                                                                                                               |

|         | haracteristics ( $I_d$ versus $V_g$ ) (b), transconductance $g_m$ versus $V_g$ (c), and                                                                                                                            |

|         | arrier field-effect mobility in the linear and saturation regime (d), (Klav                                                                                                                                        |

|         | 010)                                                                                                                                                                                                               |

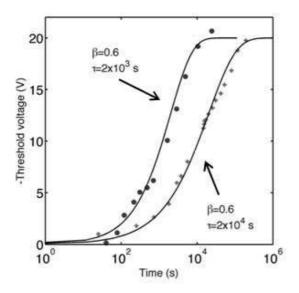

|         | igure 18: Typical bias stress curves of two OTFTs.                                                                                                                                                                 |

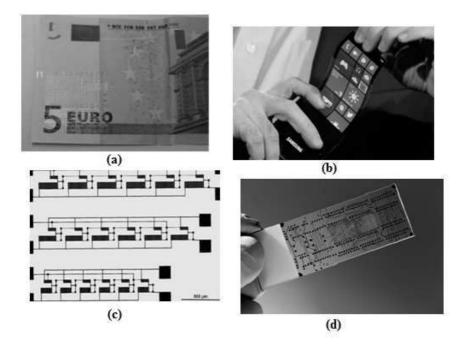

|         | <b>igure 19</b> : <i>Example of OTFTs applications: (a) banknote with OTFTs</i>                                                                                                                                    |

|         | mbedded as an anti-counterfeiting feature, (b) Samsung prototype of                                                                                                                                                |

|         | exible display, (c) organic logic circuits made by ink-jet printing, (d)                                                                                                                                           |

|         | iosensor for flexible backplanes.                                                                                                                                                                                  |

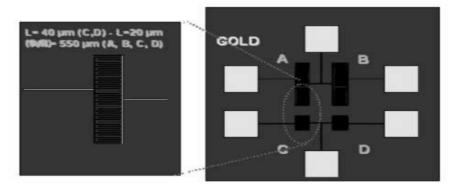

|         | <b>igure 20</b> : (right) Substrate layout and (left) magnification of the<br>nterdigitated fingers, with the specifications of the channel devices                                                                |

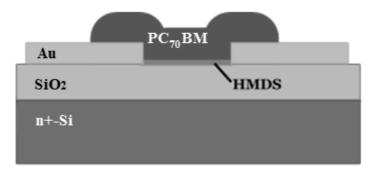

|         | <b>igure 21</b> :Schematic representation of the bottom-gate, bottom-contact                                                                                                                                       |

|         | BGBC) transistor architecture used                                                                                                                                                                                 |

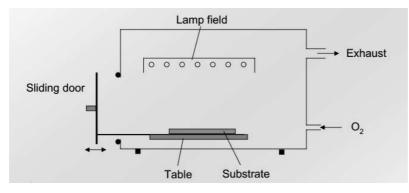

| `       | <b>igure 22</b> :Description of a $UV/O_3$ surface treatment system                                                                                                                                                |

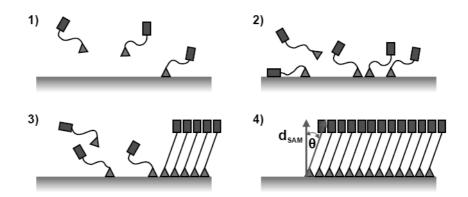

|         | igure 23: Formation mechanism of a generic SAM                                                                                                                                                                     |

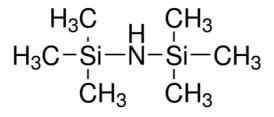

|         | <b>igure 24</b> : Chemical structure of HMDS hexamethyldisilazane                                                                                                                                                  |

|         | $(CH_3)_3Si_2NH)$ .                                                                                                                                                                                                |

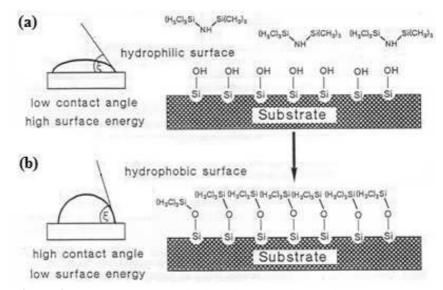

|         | <b>igure 25</b> : Formation of the hydroxyl groups during the UV/O <sub>3</sub> treatment                                                                                                                          |

| а       | substrate, (b) alkane chains during HMDS process, and the respective                                                                                                                                               |

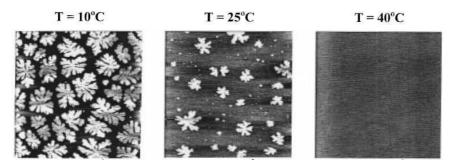

|         | ontact angles<br><b>igure 26</b> : AFM images of partial SAMs growth at temperature of 10 °C                                                                                                                       |

|         | C, and 40 °C.                                                                                                                                                                                                      |

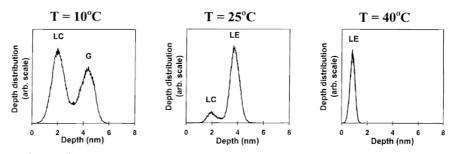

|         | <b>igure 27</b> : Depth distribution histograms for the sample at temperature                                                                                                                                      |

|         | 0 °C, 25 °C, and 40 °C.                                                                                                                                                                                            |

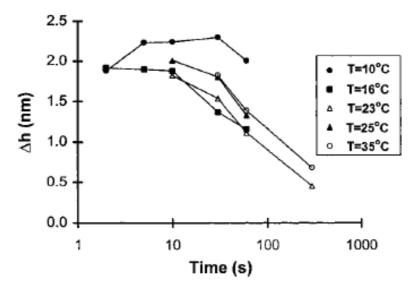

|         | <b>igure 28</b> : Average peak separation distribution, $\Delta h$ , as a function of the                                                                                                                          |

|         | me for samples processed at different temperatures                                                                                                                                                                 |

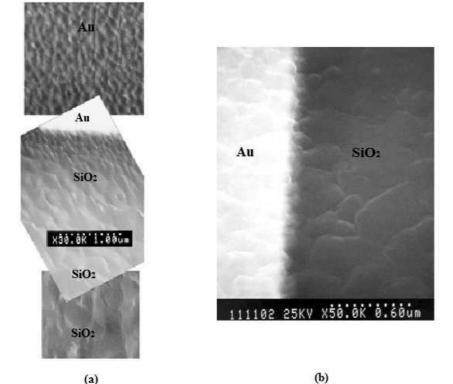

|         | <b>igure 29</b> : SEM images of a pentacene thin film grown on SiO <sub>2</sub> and on A                                                                                                                           |

| el      | lectrode: untreated with SAM (a), treated with SAM of 1-hexadecane the                                                                                                                                             |

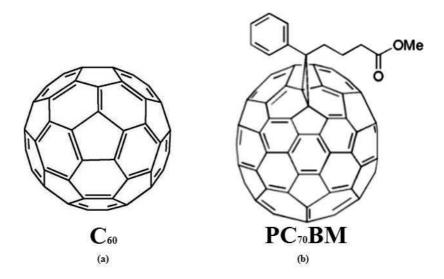

| F       | <b>igure 30</b> : Chemical structures of the fullerene $C_{60}(a)$ and fullerene                                                                                                                                   |

|         | erivate $PC_{70}BM(b)$ .                                                                                                                                                                                           |

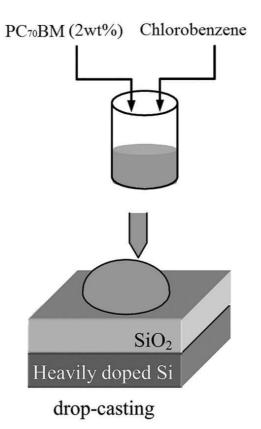

| Ľ       | <b>igure 31</b> : Description of the drop casting technique process applied in <i>hD</i> work                                                                                                                      |

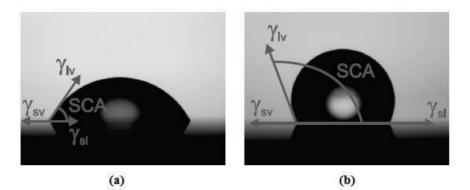

| Figure 32: Water drops on a sample surface, pre (a) and post (b) SAM                                      |

|-----------------------------------------------------------------------------------------------------------|

| deposition. The interfacial tensions and the resulting SCA are indicated in                               |

| red color                                                                                                 |

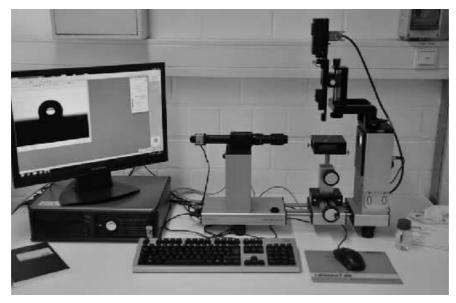

| Figure 33: Contact angle system Dataphysics OCA20 present at the ENEA                                     |

| Research Centre in Portici                                                                                |

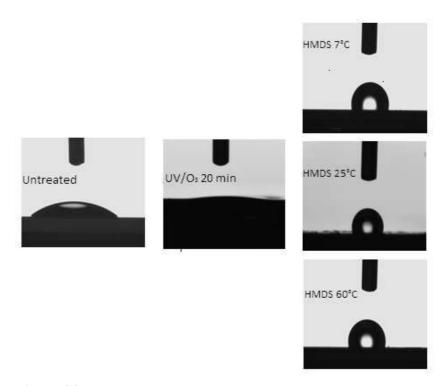

| <b>Figure 34</b> :Contact angle images for $SiO_2$ substrates treated at different                        |

| <i>HMDS deposition temperatures</i> 56                                                                    |

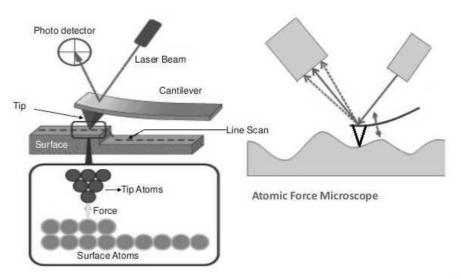

| Figure 35: Shematic diagram of the working principle of AFM 58                                            |

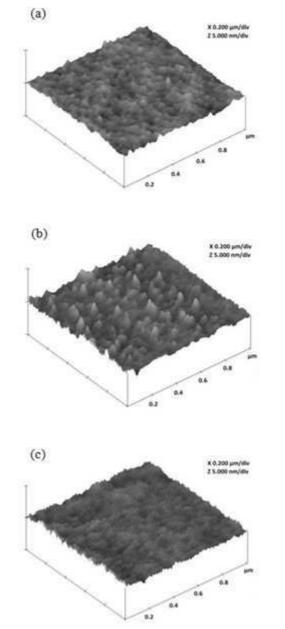

| <b>Figure 36</b> : AFM images of $PC_{70}BM$ thin films deposited on $SiO_2$ dielectric                   |

| <i>treated with HMDS: (a) at 7°C; (b) at 25°C; (c) at 60°C</i>                                            |

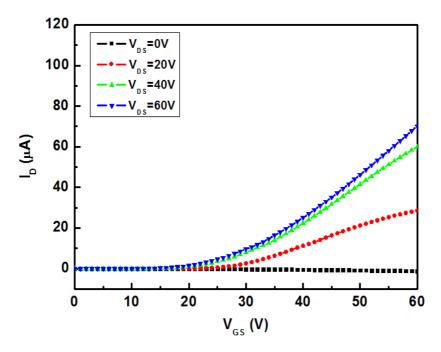

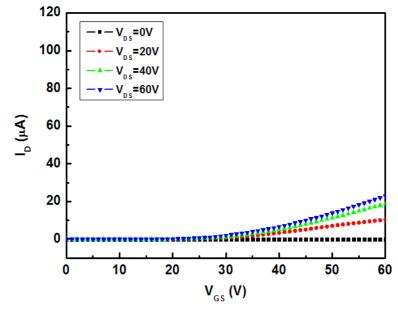

| Figure 37: Transfer curves of PC <sub>70</sub> BM based OTFTs obtained for HMDS                           |

| <i>deposition at temperature of</i> 7° <i>C</i> 61                                                        |

| Figure 38: Transfer curves of PC <sub>70</sub> BM based OTFTs obtained for HMDS                           |

| <i>deposition at temperature of</i> 25° <i>C</i> 62                                                       |

| <b>Figure 39</b> : <i>Transfer curves (b) of PC</i> <sub>70</sub> <i>BM based OTFTs obtained for HMDS</i> |

| <i>deposition at temperature of 60°C.</i>                                                                 |

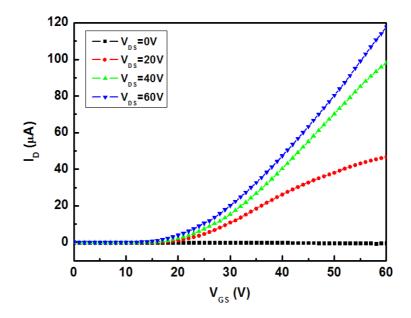

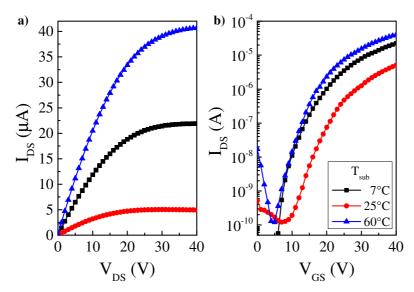

| <b>Figure 40:</b> Comparison of the output (a) and the transfer (b) curves for the                        |

| OTFTs prepared using the HMDS deposited at the three different                                            |

| temperatures; the two types of curves were respectively measured at $V_{GS}$ =                            |

| $40V and V_{DS} = 40 V.$ 63                                                                               |

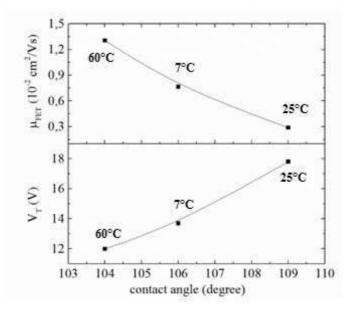

| <b>Figure 41</b> : <i>Field effect mobility and threshold voltage of the fabricated</i>                   |

| OTFTs vs. the contact angle of the substrate surface                                                      |

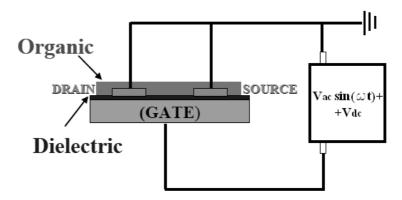

| Figure 42: Schematic diagram of the characterization set-up for the AC                                    |

| measurements of BC OTFTs                                                                                  |

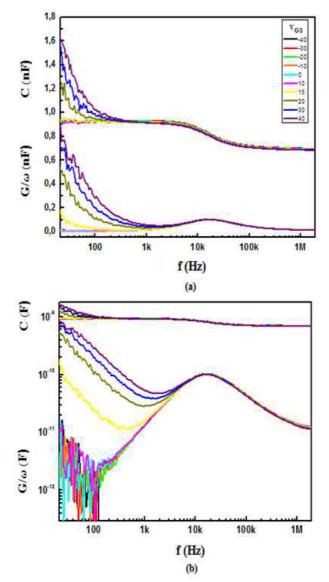

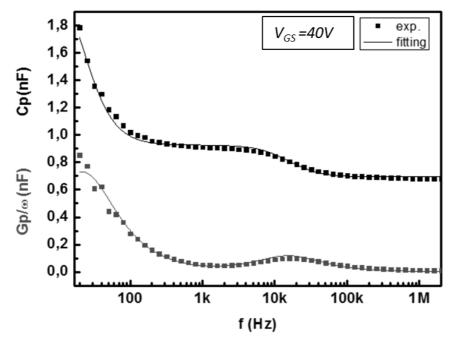

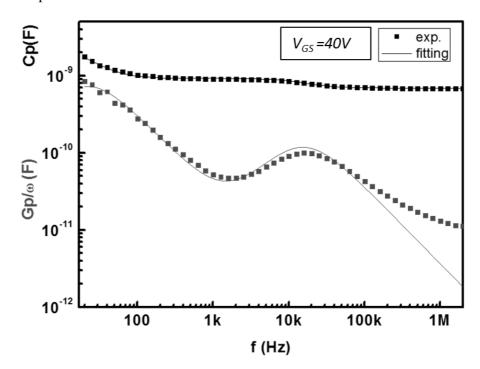

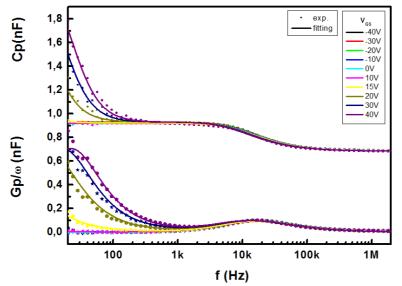

| <b>Figure 43:</b> <i>Representative capacitance and loss curves for samples at 7°C</i>                    |

| measured at various biases as a function of the signal frequency, (a) in                                  |

| linear scale and (b) in logarithmic scale                                                                 |

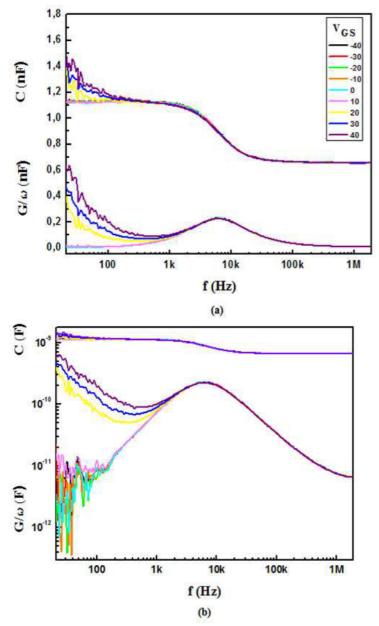

| <b>Figure 44:</b> <i>Representative capacitance and loss curves for samples at 25°C</i>                   |

| measured at various biases as a function of the signal frequency, (a) in                                  |

| linear scale and (b) in logarithmic scale                                                                 |

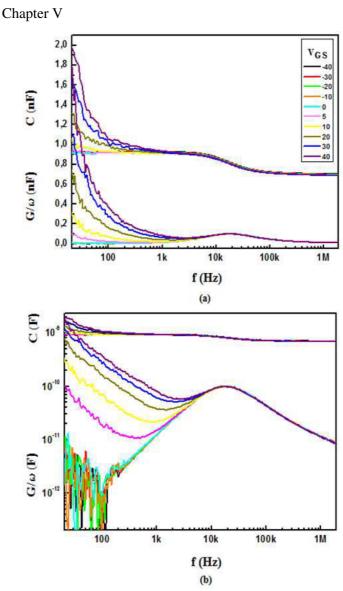

| <b>Figure 45:</b> <i>Representative capacitance and loss curves for samples at 60°C</i>                   |

| measured at various biases as a function of the signal frequency, (a) in                                  |

| linear scale and (b) in logarithmic scale                                                                 |

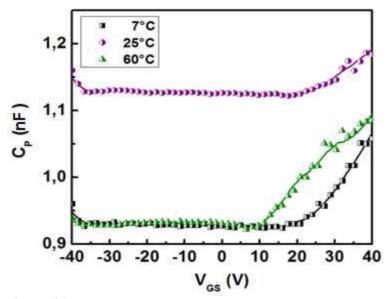

| <b>Figure 46</b> : <i>Capacitance measured as a function of the gate voltage at the</i>                   |

| fixed frequency of 100 Hz for samples at 7°C, 25°C and 60°C                                               |

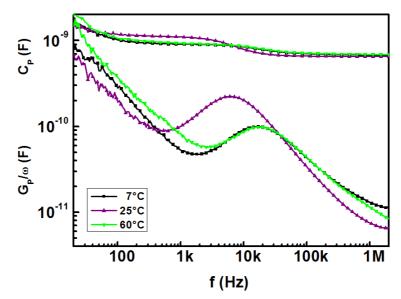

| <b>Figure 47</b> : Capacitance and loss measured as a function of the frequency at                        |

| the fixed gate voltage of 40 V for samples at 7°C, 25°C and 60°C                                          |

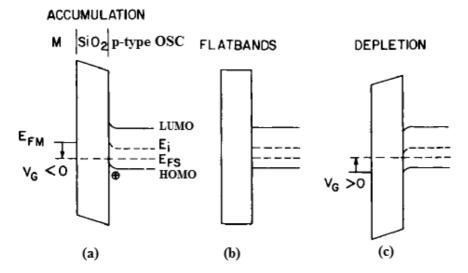

| <b>Figure 48</b> : Band-bending diagrams as a function of the applied gate bias,                          |

| considering a device with OSC of p-type: (a) accumulation regime                                          |

| (negativegate bias), (b) flat-band (no gate bias), (c) depletion regime                                   |

| (positive gate bias). HOMO e LUMO are highest occupied molecular orbital                                  |

| and lowest unoccupied molecular orbital, respectively; $E_i$ is the intrinsic                             |

| Fermi level; $E_{FS}$ is the Fermi level in the OSC; $E_{FM}$ is the Fermi level in the                   |

| metal (Nicollian & Brews, 2002)                                                                           |

| <i>Inclus</i> (11) (11) (11) (11) (11) (11) (11) (11                                                      |

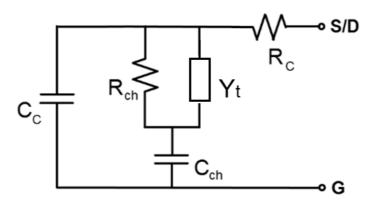

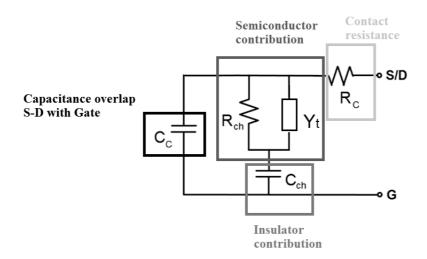

| <b>igure 49</b> : Equivalent ci | ircuit used to represent the fabricated OTFTs in                                                                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                                 | der analysis                                                                                                        |

|                                 | on of the contributions of the layers that make up the                                                              |

| ample. The equivalent c         | circuit is organized in four blocks: capacitance of                                                                 |

| verlap between S-D and          | d gate electrode, semiconductor contribution,                                                                       |

|                                 | nd contact resistance7                                                                                              |

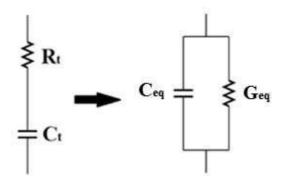

|                                 | on of the two equivalent circuits of $Y_t(\omega)$ for the                                                          |

| 0                               | vel. On the left-side, it is represented the series                                                                 |

|                                 | k, and on the right-side, the parallel combination R                                                                |

|                                 |                                                                                                                     |

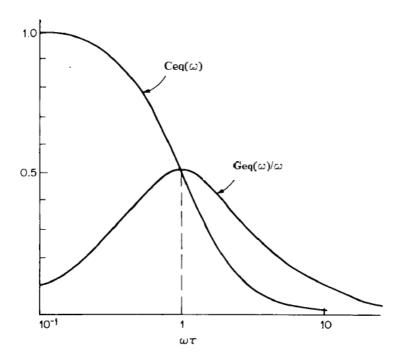

|                                 | valent trap capacitance $C_{eq}(\omega)$ and equivalent trap                                                        |

|                                 | s a functions of $\omega \tau$ derived by eq.(33) and (34)                                                          |

| 1                               | of a single trap level                                                                                              |

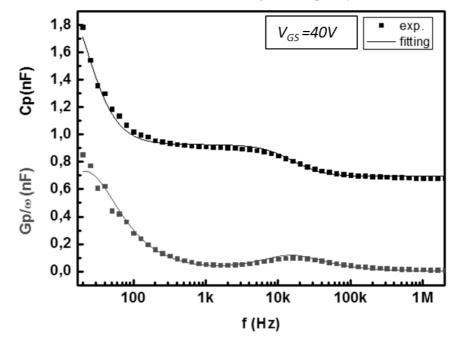

|                                 | experimental data measured at $V_{GS} = 40V$ (symbols)                                                              |

|                                 | lines) of single-level traps for the admittance of the                                                              |

|                                 | HMDS deposition temperature of 7°C. Linear scale                                                                    |

|                                 |                                                                                                                     |

|                                 | experimental data at $V_{GS} = 40V$ (symbols)                                                                       |

| 0                               | (lines) of single-level traps for admittance of traps                                                               |

|                                 | DS deposition temperature of 7 °C. Logarithmic                                                                      |

| -                               | s                                                                                                                   |

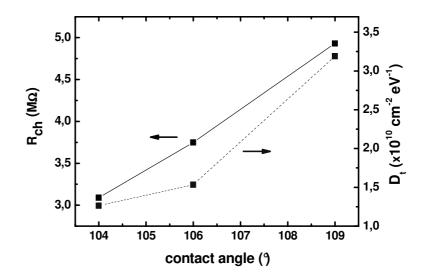

|                                 | s<br>stance $R_{ch}$ (solid line) and density of the trap states                                                    |

| 8                               | source $K_{ch}$ (solid line) and density of the trap states<br>contact angle of the surfaces of the samples treated |

| • • • •                         |                                                                                                                     |

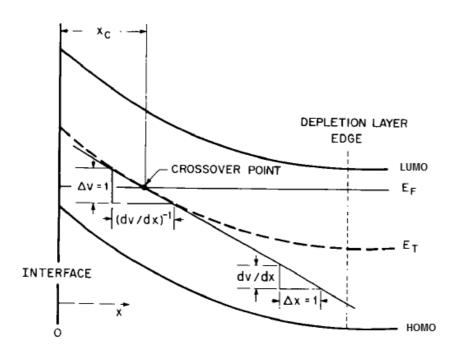

|                                 | eposition temperatures80<br>on of the band bending vs distance from the                                             |

|                                 |                                                                                                                     |

| 5                               | c semiconductor. $E_T$ is the bulk trap level (dashed                                                               |

|                                 | mi Level (solid line). This diagram shows that bulk                                                                 |

|                                 | ion of width $(dv/dx)^{-1}$ near the crossover point, that                                                          |

|                                 | n where bulk trap levels are within kT/q of the                                                                     |

|                                 |                                                                                                                     |

|                                 | rithmic scale of the equivalent trap capacitance                                                                    |

|                                 | del of a single trap level (dashed curve)as derived                                                                 |

|                                 | e model of a distribution of single trap levels (solid                                                              |

|                                 | 7. (39)                                                                                                             |

|                                 | rithmic scale of the equivalent trap conductance                                                                    |

|                                 | nodel of a single trap level (dashed curve) as                                                                      |

|                                 | d for the model of a distribution of single trap levels                                                             |

|                                 | from eq. (40). The maximum for the distributed trap                                                                 |

|                                 |                                                                                                                     |

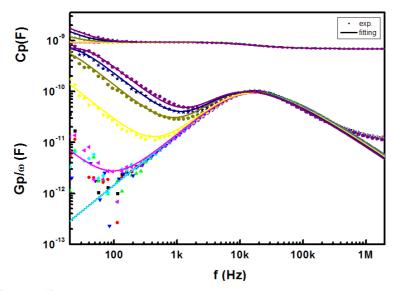

|                                 | perimental data, measured at different $V_{GS}$ (symbols)                                                           |

| ccording to the model (         | lines) of the distribution of single trap levels for the                                                            |

| dmittance of the traps f        | or the samples with HMDS deposition temperature                                                                     |

| v 1 v                           | he admittance axis                                                                                                  |

|                                 |                                                                                                                     |

| <b>Figure 60:</b> Fit of the experimental data, measured at different $V_{GS}$ (symbols), according to the model (lines) of the distribution of single trap levels for the admittance of the traps for the samples with HMDS deposition temperature at 7°C. Logarithmic scale for the admittance axis |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

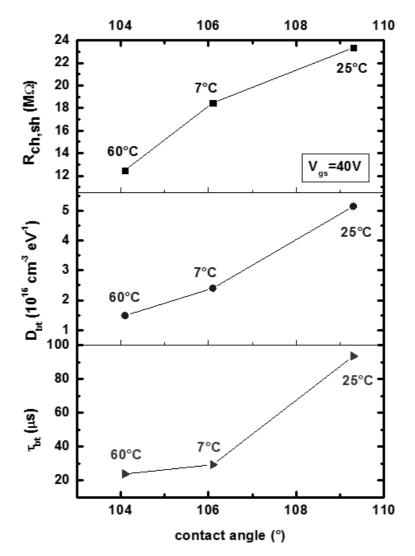

| <b>Figure 61:</b> Sheet channel resistance $(R_{ch_sh})$ , density of the trap states $(D_{bt})$                                                                                                                                                                                                      |

| and the relaxation time of the bulk trap level ( $\tau_{bt}$ ), calculated from the data                                                                                                                                                                                                              |

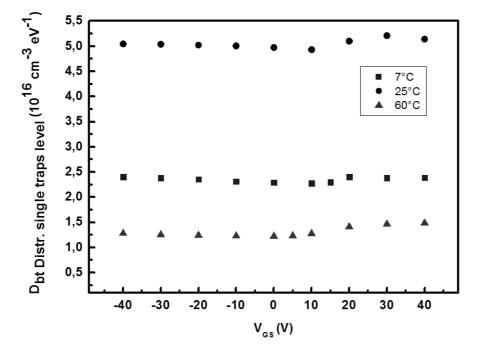

| measured at $V_{GS}$ = 40 V, vs. the contact angle of the surfaces of the samples                                                                                                                                                                                                                     |

| treated at the different HMDS deposition temperatures, according to the                                                                                                                                                                                                                               |

| model of the distribution of single trap levels                                                                                                                                                                                                                                                       |

| <b>Figure 62:</b> Trend of the density of the trap states $(D_{bt})$ as a function of the applied gate voltage $(V_{GS})$ , for all the samples treated at the different HMDS                                                                                                                         |

| deposition temperatures (7°C, 25°C, 60°C)                                                                                                                                                                                                                                                             |

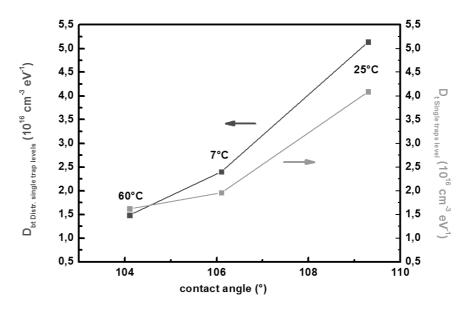

| Figure 63: Comparison of the density of the trap states for the model of                                                                                                                                                                                                                              |

| single-level traps (line orange) and for the model of a distribution of single                                                                                                                                                                                                                        |

| trap levels (line green, for $V_{GS}$ = 40V                                                                                                                                                                                                                                                           |

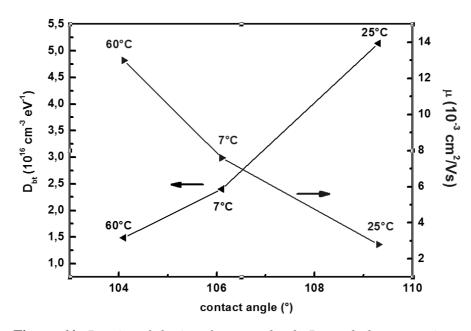

| <b>Figure 64:</b> Density of the interface trap levels $D_{bt}$ and charge carrier                                                                                                                                                                                                                    |

| mobility $\mu$ vs. the contact angle of the surfaces of the samples treated at the                                                                                                                                                                                                                    |

| different HMDS deposition temperatures                                                                                                                                                                                                                                                                |

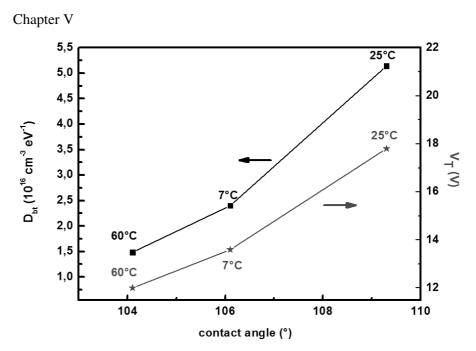

| <b>Figure 65:</b> Density of the interface trap levels $D_{bt}$ and threshold voltage $V_T$ vs. the contact angle of the surfaces of the samples treated at the different HMDS deposition temperatures                                                                                                |

|                                                                                                                                                                                                                                                                                                       |

# **List of Tables**

| <b>Table 1</b> : Summary of the surface treatment conditions and SiO <sub>2</sub> contact    |

|----------------------------------------------------------------------------------------------|

| angle values                                                                                 |

| <b>Table 2</b> : Roughness and grain mean size measurements of the PC <sub>70</sub> BM films |

| at the various $SiO_2$ surface treatment conditions                                          |

| Table 3: Electrical parameters of the OTFTs for the different HMDS                           |

| deposition temperatures (mean values and errors from 20 samples)                             |

| <b>Table 4</b> :Summary of all the components extracted from the experimental                |

| data at $V_{GS} = 40$ V according to the equivalent circuit. Extracted considering           |

| $C_c = 700 \ pF$                                                                             |

| <b>Table 5</b> : Summary of all the components extracted from the experimental               |

| data at $V_{GS} = 40$ V according to the equivalent circuit. Extracted considering           |

| <i>C<sub>c</sub> about 700 pF</i>                                                            |

### Abstract

The organic electronic devices are finding a great consideration for applications where silicon limitations make this semiconductor unsuitable. Many properties of organic materials open new frontiers of the research; some example of applications are flexible displays, smart textiles, new lighting fixtures, intelligent packaging. Furthermore, an interesting attraction of organic devices is their being environmentally friendly. Organic materials provide also an inspiration for always new applications stimulated by the continuing efforts of characterization, fabrication, synthesis and design.

This thesis work wants to contribute to the comprehension of the properties of solution processed organic thin film transistors (OTFTs) that use a n-type semiconductor. These devices are the basic element of the driving circuits, where the n channel transistors still result poorly understood. In this PhD activity, it is studied the effect of surface treatments at SiO<sub>2</sub> dielectric layer and organic semiconductor interface to improve the OTFTs performance. These transistors, that are fabricated employing a specific combination of treatments before the deposition of a soluble semiconductor, are studied in order to analyze the relationship between the surface treatments and the devices electrical parameters; so to calculate one or more variables able to better adapt the conditions of the treatments to the performances of the device.

The devices are fabricated using as semiconductor the [6,6]-phenyl-C71butyric acid methyl ester (PC<sub>70</sub>BM) deposited from drop casting technique on a SiO<sub>2</sub> layer where a combination of ultraviolet/ozone cleaning (UV/O<sub>3</sub>) and self-assembled monolayer (SAM) coating is previously carried out. The hexamethyldisilazane (HMDS) is the SAM used, and it is deposited at three different temperatures, 7°C, 25°C and 60°C. UV/O<sub>3</sub> cleaning allows to remove organic contaminations on the dielectric surface, thanks to the formation of hydroxyl groups (-OH) generated by the UV/O<sub>3</sub> ambient. While the HMDS can reduce the traps induced by Si-OH groups on the gate insulators, making layer treated hydrophobic. In this work, it is observed that different hydrophobic characters resulting in different electric performances of the devices. The techniques of analysis employed to observe the effects of the treatments have been: contact angle measurements, AFM imaging of the organic semiconductor, I vs. V static characterization and admittance measurements.

Particular effort is given to evaluate the presence of electronic trap states in organic thin film transistors based on n-type semiconductor in bottomgate bottom-contact configuration, thus it is proposed a new and accurate equivalent electrical, which is capable to model the properties of the semiconductor bulk and the conductive channel, through the calculation of the density of the trap states and the channel resistance.

From the performed analysis, the transistors treated at temperature of  $25^{\circ}$ C show a high roughness, a very inhomogeneous surface of the semiconductor layer and a higher degree of the SiO<sub>2</sub> surface hydrophobicity compared to the transistors processed at 7°C and 60°C. The HMDS behaving as a silane coupling reactant, provides a better tailored hydrophobic surface during the processes at 7°C and at 60°C, resulting in an improved surface energy, matching between the gate insulator and the organic semiconductor.

From DC measurements, it is observed that the samples at 60°C temperature for HMDS deposition show the best performances: the highest electron mobility of  $13 \cdot 10^{-3}$  cm<sup>2</sup>/Vs and the lowest threshold voltage of 12.0 V. While for the devices prepared at 7 °C and at 25 °C, the values of the mobility and the threshold voltage are 7.6  $\cdot 10^{-3}$  cm<sup>2</sup>/Vs - 13.6 V, and 2.8  $\cdot 10^{-3}$  cm<sup>2</sup>/Vs - 17.8 V, respectively.

The densities of the resulting trap states, calculated by admittance measurements and equivalent circuit, show the minimum quantity of the traps for the devices treated at 60°C compared to other devices, with a value of  $1.48 \ 10^{16} \text{ cm}^{-3} \text{ eV}^{-1}$ .

In conclusion, in this thesis it has been studied the effect of the deposition processing of HDMS layers on the behavior of  $PC_{70}BM$  bottom-gate bottom-contacts OTFTs. In particular, the temperature of the HMDS process influences the quality of the semiconductor films and the devices performances. The hydrophobicity of the dielectric surface, induced by the HDMS process at 60°C, measured trough the value of the contact angle, which is of the order of 104.1° for this process, results in the formation of the highest quality of the  $PC_{70}BM$  films, with homogeneous layers and a reduced quantity of traps, giving the OTFTs with the best performances. This results have allowed to develop a new equivalent electrical circuit, which, for the first time, models the AC behavior of bottom-gate bottom-contacts OTFTs with n-type semiconductors.

## Introduction

The Organic Electronic devices have attracted large interest in the scientific community, as evidenced by the many groups of corporate and university research centers who work on these subject, including Philips, Samsung, Sony, but also the birth of associations such as OE-A (Organic and Printed Electronics Association), which includes more than 200 companies and research centers in the world, and promotes the creation of a competitive production infrastructure for organic and printed electronics.

Organic electronics is based on the combination of a new class of materials and large-area, high-volume deposition and patterning techniques. The peculiar mechanical properties of organics, the easiness of device manufacturing and the cheapness of the end products open the way to a wide range of applications, from flexible displays, to smart-card, up to wire devices for intelligent fabrics (smart clothing).

This technology is still in its early stage; while increasing numbers of products are available and some are in full production, many applications are still in lab-scale development, prototype activities or early production (Kirchmeyer et al., 2013).

The future of organic electronic is based on devices that are able to do things that are not possible for silicon-based electronics, expanding the functionality and accessibility of electronics, as the ability to create flexible and transparent devices. Organic electronic devices will be more energyefficient than today's electronics, and will be manufactured using more resource-friendly and energy efficient processes than today's methods, contributing to a more sustainable electronic world.

Actually, many efforts have been done in order to develop the organic driving circuits, such as switches and memories, required for implementing a fully flexible, plastic electronics. In particular, for this aim, the interest is focused on solution processed organic thin film transistors (OTFTs) that could be the backbone of the plastic electronics.

A significant technological challenge is associated with the fabrication of organic complementary circuits, where deposition and patterning of the pand n-channel semiconductors with high resolution is the objective pursued. The vast majority of organic complementary circuits reported in the literature to--date are based on thermally evaporated p-channel/n-channel semiconductors. But, a proof of concept of the practical implementation of this technology in large-scale ICs is limited due to design constrains imposed by the shadow masks utilized for the semiconductor patterning. In this context, alternative deposition techniques (i.e. ink-jet printing, gravure printing, etc.) could potentially provide a long-term solution. In an effort to address this issue, significant research has focused on the organic semiconductors with useful solubility. As a result, a number of soluble p-channel semiconductors with carrier mobility comparable to amorphous silicon (a-Si) have been demonstrated and utilized in unipolar ICs. On the other hand, progress in the area of soluble n-channel semiconductors has been much slower with relatively few successful demonstrations. This distinct lack of soluble n-channel semiconductors has, to a large extent, hindered the development of large-scale organic complementary ICs (Wobkenberg & Anthopoulos, 2008).

In this context, this thesis work regards the fabrication of n-type OTFTs using the fullerene derivative [6,6]-phenyl-C71-butyric acid methyl ester ( $PC_{70}BM$ ) as the semiconductor. This molecule is soluble in various organic solvents, allowing an easy deposition from solution and so being potentially much advantageous in the area of the large-area organic electronics.

The aims of the present research are the realization of n-type transistors with solution processed semiconductor to obtain good performance, as well as the understanding and the modeling of the mechanism involved in these unconventional materials.

A critical issue to be investigated in order to obtain good-performance OTFTs is the quality of the interfaces between the various layers constituting the device, particularly the interface between the semiconductor and the gate insulator, where the conductive channel is generated. For this purpose, in this work different processes are considered to improve the performance of the OTFTs, that are: the wafer cleaning procedures using an UV/O<sub>3</sub> treatment, the application of surfaces modification using a self-assembled monolayers (SAM), and different temperatures during the depositions of SAM layer.

Static electrical measurements and AC electrical techniques have been borrowed by the world of the inorganic semiconductors in order to evidence all the aspects regarding the features of the organic semiconductors and the devices based on them. DC measurements represent a basic tool for the analysis of the properties of organic semiconducting materials, while AC electrical techniques give the possibility of probing the local contributions to the observed overall properties showed by organics and devices, such as the limiting charge trapping phenomena due to extrinsic localized defects and the trapping produced by the intrinsic defects due to the structural features of the active organic materials, which are limiting factors in terms of OTFTs performance. To model these aspects, an electrical equivalent circuit was proposed to interpret the data of the admittance measurements. This new RC network includes all the effects of OTFTs in bottom-gate bottom-contacts configuration and well describes the properties of dielectric/organic semiconductor ( $SiO_2/PC_{70}BM$ ) interface.

In this context, the thesis work proposal regards the study of the interface and the related devices properties through the analysis of the grade of wettability of the dielectric surface after SAM deposition at different temperatures, the morphological analysis of the semiconductor layer in different conditions, and the application of both the methods of static and dynamic analysis of the electrical measurements.

The thesis is organized in five chapters. In the Chapter 1, it is presented a brief historical framework of the organic semiconductors, an overview on the principal features of the organic semiconductors and on their future applications. The Chapter 2 is dedicated to the organic thin film transistors, focusing the attention on ideal and non-ideal functioning principles, the devices architecture, the description of the extracted device parameters, the difference between p-type and n-type transistors, and possible new implementations of these devices. In the Chapter 3, it is described the fabrication process used to realize the samples and their analysis respect on some important parameters, as temperature and time. In particular, it is presented the architecture employed, the steps for the fabrication of the devices and drain electrodes and deposition of the organic semiconductor. All activities carried out during the PhD activity are deal with in the Chapters 4 and 5..

The experimental work was carried out at the ENEA Research Centre in Portici and in the Microelectronics Laboratory of the University of Salerno. All the fabricated devices have been processed in the cleanroom (class 100) located in ENEA, while the electrical characteristics are analyzed both at the ENEA and at University. The Chapter 4 is devoted to describe in detail the results of the experimental analysis to evaluate the fabrication processes adopted. Measurements of the contact angle and the semiconductor films morphology are part of this chapter. Furthermore, the results of the static characterizations of the OTFTs are presented. Thus, a part of the chapter is focused on the hydrophobic characteristics of the devices, with particular attention on the relationship between the grade of wettability and the devices performance. In the Chapter 5, the AC measurements of the devices admittance and a new model of the OTFTs AC behavior are presented. This model takes into account the devices geometry and the distribution of the traps levels in disordered semiconductors. The purpose of the proposed model is to evaluate the effect of the different treatments by extracting some interesting parameters that allow to compare them. Then, two models of the admittance associated with the traps are reported, together with fitting data and extracted parameters associated, respectively, to deepen the understanding of the traps behavior in this type of semiconductors and devices. Finally, the AC parameters are compared with the resulting parameters of the DC measurements, to understand the efficacy of the treatments to improve the overall performance of the studied transistors.

## Chapter I Organic Semiconductors

In 1977 a new class of materials was discovered, their name was 'conducting polymers' (Shirakawa et al., 1977). These materials, now known as organic semiconductors, obtained significant interest of scientific communities in their properties and applications. This research consisted on the observation of increased electrical conductivity of halogen-doped polyacetylene, and for this work, Heeger, MacDiarmid, and Shirakawawere awarded the 2000 Nobel Prize in Chemistry.

In 1986 started the first applications of organic semiconductors: Tang reported a two-layer organic photovoltaic cell (OPV) using copper phthalocyanine (CuPc) and a perylenetetracarboxylic derivative as organic semiconductors (Tang, 1986) and, in the same year, an organic field-effect transistor (OFET) using polythiophene was first reported by Tsumura, Koezuka, and Ando (Tsumura et al., 1986). In 1987, Tang and VanSlyke realized organic light-emitting diodes (OLEDs) using an Alq3/diamine junction (Tang & VanSlyke, 1987). Even if the devices did not exhibit great performances, they were recognized as milestones about the electronic application of organic semiconductors, which lasts until present and is foreseen a very bright future.

The peculiarities of organics are given by their molecular nature, by weak intermolecular interaction. While for inorganic crystals all consisting atoms are strongly bound by covalent bonds, for organics the molecules are 'weakly' linked to each other by van der Waals force (Brown & Poon, 2004). Thus, this weak intermolecular interaction is responsible for the mechanical flexibility of the organic films or crystals. Furthermore, weak molecule-molecule bonds can be easily broken or reformed so molecules can be dispersed in solvents or evaporated at moderate temperature, allowing for various new process concepts for the organic semiconductors.

In this first chapter, it is shown a review on the fundamental physics and mechanism of charge injection into organic semiconductors (OSCs), and moreover a brief digression on defects and current and future applications.

#### I.1. Physics of Organic Semiconductors

Organic materials are characterized by building blocks made up by various forms of hydrocarbon (C-H) units, which can also include heteroatoms such as nitrogen, sulfur, oxygen, etc (Brown & Poon, 2004). For their typical energy gap ranges (between 1.5 eV and 3.5 eV) and their few mobile or free carriers at room temperature, organic materials can be considered as insulators. But the organic materials can be defined as organic semiconductors that exhibit semiconducting properties, and corresponding to a subset of a vast variety of organic materials.

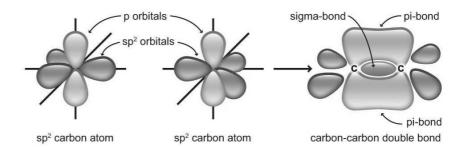

Carbon is a chemical element in the fourth group of the periodic table, so it contains four valence electrons. The electronic orbitals of a carbon atom may hybridize differently, depending on the number of atoms with which the valence electrons are shared (Kymissis, 2009). The valence electrons can be shared with four neighboring atoms, to form four chemical bonds and four equivalent degenerated orbitals, referred to as sp<sup>3</sup> hybrid orbitals in a tetrahedral orientation around the carbon atom. Four sp<sup>3</sup> hybrid orbitals of equal energy are created by the superposition of one 2s and three 2p orbitals. It is also possible that only three chemical bonds are formed, so they have three coplanar  $sp^2$  hybridized orbitals with one remaining  $p_z$  orbital. Three electrons of a carbon atom in the sp<sup>2</sup> orbitals are called  $\sigma$ -bonds, and are associated with a highly localized electron density in the plane of the molecule. The one remaining free electron per carbon atom resides in the p orbital, perpendicular to the plane of the  $sp^2$  hybridization, to form so-called  $\pi$  -bonds (Fuchigami et al., 1993), (Matters et al., 1999). A schematic representation of the  $sp^2$  hybridization and the formation of carbon-carbon double bonds is exemplified in Figure 1.

**Figure 1**: Schematic representation of the formation of  $\sigma$  and  $\pi$  molecular orbitals from two carbon atoms with sp<sup>2</sup> hybridization.

Due to the large overlap between the orbitals,  $\sigma$  bonds are strong and difficult to be broken because they have a high binding energy. Instead, the

$\pi$  bond has significantly lower binding energy than the  $\sigma$  bond, because the distance between the two p<sub>z</sub> orbitals is considerable, which means weak overlap or interaction between these orbitals; in this case, the electrons can be delocalized over several adjacent atoms. Thus, this weak  $\pi$  bond, or this delocalization of the electrons, makes it simple to displace electrons using an electric field, and then accounts for the semiconducting properties and the special characteristics of the organic molecules, as mechanical softness and solution-process compatibility that are the main advantages of weakly-bound molecules.

To describe the electronic energy levels, in the inorganic semiconductors, valence band and conduction band are considered, while for organic semiconductors exist similarly Highest Occupied Molecular Orbital (HOMO) and Lowest Unoccupied Molecular Orbital (LUMO). HOMO is the energy level at the top of a continuous band of occupied states, whereas LUMO is the first available energy level in the unoccupied band. The HOMO-LUMO gap is relatively small, due to the weak  $\pi$  binding energy. Therefore, organic materials can be considered as semiconductors due to the possibility to have a significant density of thermally-generated and/or photogenerated charge carriers. Delocalization of the electrons in the  $p_z$  (or  $\pi$ ) orbitals implies the possibility of the movement of charge carriers inside a molecule, whereas the electrons forming  $\sigma$  bonds serve as a rigid frame that maintains the structure of the molecule. The electrons, loosely bounded and delocalized inside a molecule, are responsible for the electrical conduction. This type of chemical system where the  $\pi$ -electrons are delocalized through alternating single and double bonds is often called a  $\pi$ -conjugated system. In general, the  $\sigma$  and  $\pi$  bonds are defined intramolecular bonds which bind atoms to form a single organic molecule, while the van der Waals forces are the intermolecular interactions, that are very weak and the overlap of wave functions centered on neighboring molecules is very small (Schwoerer & Wolf, 2007).

#### I.2. Charge transport mechanisms

For the organic molecules, the fundamental property that allows for semiconducting properties at molecular level is the  $\pi$  conjugation. An example is the presence of alternating single and double bonds between covalently bound carbon atoms. Therefore, in organic solids, semiconducting properties at macroscopic level is only expected when the intermolecular interaction is significant, so that the  $\pi$ -electrons can have enough freedom to be delocalized and move from one molecule to another.

Because the intermolecular bonds in organic solids are due to relatively weak van der Waals interactions, the electronic wave functions usually do not extend over the entire volume of the organic solid, but are localized to a

finite number of molecules, or even to individual molecules. In this way, the charge transport through the organic semiconductor is limited by trapping in localized states, which means that charge carriers mobility  $\mu$  in organic semiconductors is usually low and is expected to be thermally activated. Furthermore, most of the organic semiconductors are amorphous and rich in structural and chemical defects, therefore conventional models for charge transport must be adapted and extended; moreover, charges can move, with different mobility, within the molecular chain (intra-chain), between adjacent molecules (inter-chain), or between different domains, generally referred as grains (inter grain). The nature of the charge transport is still controversial, but several different models for charge transport in organic semiconductors have been developed, some of which will be discussed in the following.

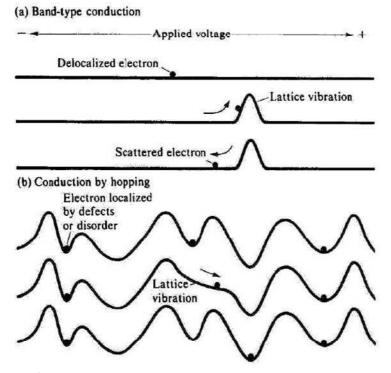

The charge carrier transport mechanism can fall between two extreme cases: **band transport** and **hopping transport**. The band transport model assumes drift of charge carriers upon an applied electric field by repeated acceleration and collision with the lattice by which they totally lose their energy. This process is usually modeled by  $\mu \sim T^n$  with n > 0 (Sze & Ng, 2007), where *T* is the absolute temperature. A temperature dependence of mobility is exhibited, along with a dependence on the applied electric field. In the band type conduction, electrons are scattered by lattice vibration, so that mobility decreases with increasing temperature, as illustrated in Figure 2(a).

Organic Semiconductors

**Figure 2**: Representation of the transport mechanism in solids with applied electric field, (a) for band transport conduction and (b) for hopping between localized states.

The presence of the defects and the non-crystalline structure of the organic materials lead to the formation of localized states. In this case the transport can be described by **the hopping between** localized states. Transport is thermally activated as  $d\mu/dT > 0$  because the lattice vibration helps localized charges to overcome potential barriers, Figure 2 (b).

Several charge transport models have been developed for the hopping motion. The **Poole-Frenkel model** (Frenkel, 1938) explains the increase of conductivity in insulators and semiconductor when high fields are applied. This model describes well the charge transport in many organic systems, and the charge carrier drift mobility has the form:

$$\mu = \mu_o exp^{(\beta_{PF} \sqrt{F})} \tag{1}$$

where  $\mu_0$  is the zero-field mobility, *F* the applied electric field and  $\beta_{PF}$  the Poole-Frenkel slope.

In the **model of variable range hopping (VRH)** the charge carrier is highly localized. In order to conduct, charge carriers hop between these localized electronic states by quantum-mechanical tunneling and overcome

the energy difference between them, emitting or adsorbing phonons during intra-chain or inter-chain transitions. In 1998, Vissenberg and Matters (Vissenberg & Matters, 1998) developed a theory for determining the mobility of the carriers in transistors with amorphous organic semiconductors. They pointed out that the transport of carriers is strongly dependent on the hopping distances as well as the energy distribution of the states. At low bias, the system is described as a resistor network, assigning a conductance  $G_{ij} = G_0 exp (-s_{ij})$  between hopping site *i* and the site *j*, where  $G_0$  is a prefactor for the conductivity and  $s_{ij}$  is defined as in eq.(2)

$$s_{ij} = 2\alpha R_{ij} + \frac{|E_i - E_F| + |E_j - E_F| + |E_i - E_j|}{2kT}$$

(2)

where k is the Boltzmann constant and T is the absolute temperature.

The first term in the eq.(2) describes the tunneling process, which depends on the overlap of the electronic wave functions of the sites *i* and *j*,  $E_F$  is the Fermi energy and  $E_i$  and  $E_j$  the energies of the sites i and j. In a lowest-order approximation, this tunneling process may be characterized by the distance  $R_{ii}$  between the sites and an effective overlap parameter  $\alpha$ . The second term takes into account the activation energy for a hop upwards in energy and the occupational probabilities of the sites i and j. Starting from this expression, with the percolation theory, they can relate the microscopic properties of the organic semiconductors to the effective mobility of the carriers in a transistor. Specifically, carriers either hop over short distances with large activation energies, or over long distances with small activation energies. Since the hopping is thermally activated, the mobility increases with increasing temperature. With increasing gate voltage, carriers accumulated in the channel fill the lower-energy states, thus reducing the activation energy and increasing the mobility. The tunneling probability depends strongly on the overlap of the electronic wave functions of the hopping sites. This result is consistent with the observation that the carrier mobility is significantly greater in semiconductors characterized by a larger degree of overlap of the delocalized molecular orbitals of neighboring molecules. Thus, the mobility is dependent on temperature, gate voltage, and molecular arrangement in the solid state.

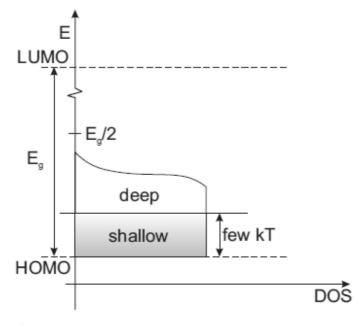

In contrast to the variable range hopping model, the **multiple trapping** and release (MTR) model was extended to organic semiconductors by Gilles Horowitz and co-worker (Horowitz et al., 1995). The model assumes that charge transport occurs in extended states, but that most of the carriers injected in the semiconductor are trapped in states localized in the forbidden gap, and that carriers cannot move directly from one state to another. These traps, that are associated with structural or chemical defects, can be *deep*, if their energy level is near the middle of the band gap, or *shallow*, if they are located near the conduction or valence band. An example of the distribution of these types of energy levels is shown in Figure 3.

**Organic Semiconductors**

**Figure 3**: Distribution of trap states in the band gap for a p-type organic semiconductor.

Thus, carriers are temporarily promoted to an extended-state band in which charge transport occurs.

The model shows a dependence of the mobility of the carriers on temperature, on the energetic level of the traps, as well as on the carrier density and therefore on the applied voltage to a device. For a single trap level with energy  $E_{tr}$  the drift mobility is:

$$\mu_{D} = \mu_0 \alpha exp^{\left(-\frac{E_{tr}}{kT}\right)} \tag{3}$$

where  $\mu_0$  is the mobility in the delocalized band,  $\alpha$  is the ratio of the effective density of state at the delocalized band edge to the concentration of traps.

Although the existence of an extended-state transport band in organic semiconductors, as postulated by the MTR model, is often debated, the MTR model appears to properly describe transport in organic semiconductors with a microstructure that favors a high degree of intermolecular orbital overlap, such as polycrystalline films of small-molecule and certain polymeric semiconductors with room-temperature mobility that approach or exceed 0.1 cm<sup>2</sup>/Vs (Klauk, 2010). Indeed, quantum-mechanical calculations (VRH) of the charge-carrier dynamics in defect-free pentacene crystals suggest that carriers propagating through the molecular lattice under the influence of an

external electric field are delocalized over a significant number of molecule, and that the carrier drift velocity is within a factor of two of the saturation velocity in single-crystalline silicon (Hultell & Stafstrom, 2006).

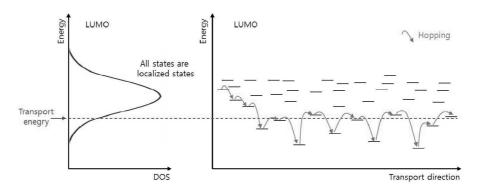

Further theory for hopping charge transport is the **Gaussian disorder model** (GDM) proposed by Bassler (Bassler, 1993), and widely used for solids where the degree of disorder is high, where 'strong localization' results in the absence of extended band states. In this model, all electronic states have to be regarded as localized states, and their energetic distribution is described by a Gaussian distribution, Figure 4.

**Figure 4**: Hopping transport through the localized states in the Gaussian disorder model (GDM).

The major characteristics of this model are the non Arrhenius temperature behavior and the dependence of the mobility on the electric field. The expression for the GDM mobility can be written as:

$$\mu(F,T) = \mu_{\infty} exp^{\left[-\left(\frac{2\sigma}{3kT}\right)^2\right]} exp^{\left(\beta\sqrt{F}\right)}$$

<sup>(4)</sup>

where  $\mu_{\infty}$  is the high temperature limit of the mobility,  $\sigma$  is the energetic disorder, related to the half-width of Gaussian DOS (density of states) and  $\beta$  is a factor depending on the geometric randomness arising from structural or chemical defects.

Another model commonly believed to be suitable to describe transport mechanism in organic materials is the **grain boundary model** that explains the trap limited currents, which are presumably caused by traps located at grain boundaries. This model uses thermionic emission and assumes that charge states at the grain boundary present an electrostatic barrier to carrier transport, but charges within the grain screen the potential, reduce the barrier and increase the effective mobility (Steudel et al., 2004), (Shang et al., 2006) and (Verlaak & Heremans, 2007). The direct correlation of potential drops and grain boundaries has been visualized with Kelvin probe microscopy

(KPM) (Ohashi et al., 2007) and phase-electrostatic force microscopy (Annibale et al., 2007). Inhomogeneous voltage drops have further be seen for slightly contaminated gate oxides with KPM, while pure SiO<sub>2</sub> substrates show a homogenous voltage drop of up to 85% over the channel (Luo et al., 2007). Thermionic-emission over a Schottky contact barrier has also been used to explain the temperature dependence of the charge carrier mobility in rubrene single crystals, revealing two segments supposed to be described by the intrinsic polaronic transport above 150 K and the trap-dominated conduction below, resulting in a decreasing mobility with lower temperatures (de Boer et al., 2004).

### I.3. Charge carrier injection

A physical behavior that strongly influence the amount of charge carriers injected into an organic semiconductor is the injection barrier at the metal electrodes/active layer interface. The barrier height strongly depends on the energy level matching between the Fermi level of the electrode material and the organic semiconductor energy levels, the HOMO or LUMO level of the organic semiconductor, for holes and electrons respectively.

One of the fundamental aspects of the metal/semiconductor interface is the Fermi level alignment, described by the Mott-Schottky model (Sze, 1981). When a neutral metal and a neutral semiconductor are brought in contact, the Mott-Schottky model predicts that their bulk Fermi levels align, causing the band bending in the semiconductor. In the Mott -Schottky limit, the vacuum level of the organic material and of the metal align, forming a region of net space charge at the interface, as depicted in Figure 5(a). However, the Mott-Schottky limit is rarely observed at real metal/organic interfaces due to the formation of a strong interfacial dipole  $\Delta$  between the metal surface and the organic molecules, which tends to pin the Fermi level, Figure 5(b). The origin of the interface dipole is attributed to several mechanisms; charge transfer across the interface, formation of induced or permanent dipoles into the organic layer, chemical interaction, and presence of interface states (Miozzo et al., 2010).

**Figure 5**: Schematic energy level diagram of the band alignment at a metal organic interface, (a) Mott-Schottky limit vacuum level alignment, and (b) pinning of the Fermi level by induced interface states interfacial dipole.

An effective metal work function  $\Phi_{m,eff}$  can be defined as the difference between the pristine metal work function  $\phi_m$  and the dipole(Helander et al., 2008),

$$\Phi_{m,eff} = \Phi_m - \Delta \tag{5}$$

For the inorganic semiconductors, Heine (Heine, 1965) demonstrated that surface states do not exist in the forbidden gap of most of them but gap states are induced in the semiconductor as a result of the rapidly decaying tail of the electronic wave function from the metal. These metal induced gap states are independent of the energy levels in the semiconductor, and hence can either be donorlike or acceptorlike when close to the valence or conduction bands, respectively. A charge neutrality level  $E_{CNL}=e \phi_{CNL}$  is defined as the point at which the interface states are equally donorlike and acceptorlike. Therefore, at metal/semiconductor interfaces the charge neutrality level of the semiconductor will tend to align with the Fermi level of the metal as a result of charge transfer between the metal and the induced gap states, forming an interfacial dipole (Cowley & Sze, 1965),

$$\Phi_{m,eff} = \Phi_{CNL} + S_{\Phi}(\Phi_m - \Phi_{CNL}).$$

(6)

Here, the interface slope parameter  $S_{\phi}$ , for weakly interacting interfaces, was empirically found by Mönch (Mönch, 1987) to depend on the optical dielectric constant,

Organic Semiconductors

$$S_{\Phi} = \frac{1}{1 + 0.1(\varepsilon_{\infty} - 1)^2} \tag{7}$$

where  $\varepsilon_{\infty}$  is the optical dielectric constant (high frequency limit of the dielectric function). Mott-Schottky model is generally used to choose the contact metal to not limit the performances of a device because of non-ohmic contacts. In the case where the density of interface states is very high, a Fermi-level pinning can take place, and the injection barrier becomes independent on the metal workfunction: it means that contact metal has no importance for the resulting injection barriers (Koch & Vollmer, 2006). This phenomenon accounts for an important implication for organic devices: they should generally bear a substantial injection barrier that cannot vanish below a certain level determined by the position of the pinned Fermi level.

Another important aspect that can have a strong influence in charge injection, is the presence of traps at the metal/organic interface, which are mostly produced during contact fabrication (Dimitrakopoulos & Mascaro, 2001). The deposition of the metal contacts can cause local damages in the structure of the material, due to the diffusion of the deposited specie into the active layer. On the other hand, the deposition of the organic material on top of the metal electrodes can lead to an accumulation of structural defects.

#### I.4. Defects in organic semiconductors

The electrical behavior of the organic materials is strongly influenced by the presence of trap states, which modify the number of the charges in the energy bands and the stability of the materials themselves. Charge carrier traps can be caused by structural defects or impurities. The structural defects are classified in: native point defects (as a vacancy), or interstitials, or extended defects (like edge dislocations, screw dislocations, or grain boundaries). Structural defects can lead to energy levels in the band gap. Some traps are electrically neutral when empty and become charged upon trapping a charge carrier. On the other hand, some defects are called antitraps because result in scattering centers, but do not cause traps (Klauk, 2006).

Organic materials are very sensitive to chemical impurities, which modify the number of the charges in the energy bands. In some cases, it is performed an artificial addition of chemical impurities which have different energy levels than the host material, and in Figure 6 is illustrated a simple scheme useful to understand the positions of electron and hole traps, respectively  $E_t^e$  and  $E_t^h$ , into a host material.

**Figure 6**: *Representation of the energy levels of a host material with chemical impurities* (Pope & Swenberg, 1999).

In Figure 6  $\Delta E_t^e$  and  $\Delta E_t^h$  represent the traps depths for electrons and holes, while  $(A_c)_{guest}$  and  $(A_c)_{host}$  are respectively the electron affinity of the guest and of the host materials and  $(I_c)_{guest}$  and  $(I_c)_{host}$  are their ionization energies. The electron trap depth can be approximated with the difference in electron affinity of the host and guest materials and written as (Pope & Swenberg, 1999):

$$\Delta E_t^e \approx (Ac)_{guest} - (Ac)_{host} \tag{8}$$

In a similar way, the hole trap depth is described as:

$$\Delta E_t^n \approx (lc)_{host} - (lc)_{guest} \tag{9}$$

However, the atoms or molecules of the added impurity may deform the host lattice due to a different size, and may change the polarizability of the lattice in local. In presence of an impurity larger than the host molecule, a compression of the lattice and an increase in polarization energy result in the host, and traps located on host molecules adjacent to the chemical impurity. On the contrary, a small polarization energy results for a smaller impurity, so that the charge transport is impeded (Pope & Swenberg, 1999).

Defects can be introduced into materials also under ambient conditions, because of the presence of light, oxygen and water. For example, the adsorbed water on the gate dielectric can dissociate and react with organic semiconductor so that water molecules are able creating hydrogen bonds retained responsible of charge transport. An example of the oxygen effect on pentacene transistor characteristics is shown in Figure 7: a transistor is measured as grown, kept in high vacuum, and after oxygen, that is the same device was measured after the oxidation process.

**Figure 7**: Transfer characteristic of a pentacene transistor measured as grown (blue line) and after oxidation (red line). The graph shows the forward and the reverse sweeps in both cases.