# Project and Development of Hardware Accelerators for Fast Computing in Multimedia Processing

Cappetta Carmine

# **UNIVERSITY OF SALERNO**

# DEPARTMENT OF INDUSTRIAL ENGINEERING

Ph.D. Course in Industrial Engineering Curriculum in Electronic Engineering - XXXI Cycle

# PROJECT AND DEVELOPMENT OF HARDWARE ACCELERATORS FOR FAST COMPUTING IN MULTIMEDIA PROCESSING

**Supervisor**

Prof. Gian Domenico Licciardo

Ph.D. student

Carmine Cappetta

# **Scientific Referees**

Prof. Nicola Petra

Prof. Maurizio Martina

Ph.D. Course Coordinator

Prof. Ernesto Reverchon

Ma rimasi nascosto,

Passarono a stanarmi,

Tornai a muovermi

Rimanendo al buio.

Mi insegnarono a vedere,

A riconoscere la tecnica,

Poi anche l'arte.

Mi mostrarono la cima,

Capovolsero la prospettiva,

Ero ancora acerbo.

Ora punto solo a migliorare

Provando a preferire

Che la ragione sia altrui.

# Acknowledgments

The development of this work and the personal growth that come with it has been possible thank to many people.

First, I would like to thank Prof. Gian Domenico Licciardo for the help and the chances he gave to me, and, moreover, his suggestions and encouragement. A special thank goes also to Luigi, who not only helped me, but also put up with me, which is no easy task. With him I cannot forget to thank also Prof. Alfredo Rubino, Rosalba and Antonio for the kindness and their time. I would also like to thank Prof. Salvatore Bellone, because without his teaching I would not be here and I would not have chosen a PhD course; moreover, I would have been a completely different engineer and person.

Huge thanks goes also to Giuseppe and Thomas for the period at STMicroelectronics. Together with their group, they have not only accepted me, but made me feel comfortable and taught me how to move in a different environment from the university one. Last year changed a lot my perspectives and my way of thinking.

I would not be the man I am without my family, hence a particular thank goes to my mother, Helga, who is often too caring towards me even if I could be detached or annoying, my father, Donato, who somehow manages to find always the right words to take out the best out of me, and my sister, Gina, who helped me in so many ways she could not imagine. With them there is also a great supporting cast made up by my grandparents, my uncles and cousins.

A lot of people say that friends are the family you choose, so I have to thank also: Aika, Alessia, Alessio, Alfonso, Carmen, Dario, Ece, Emanuele, Emilio, Flora, Francesco, Giovanni, Luca, Maria Alfonsa, Marianna, Mattia, Mehmet, Michele, Monica, Nicola, Raffaele, Rino, Roberto, Rosa, Sarah, Serena, Tommaso, Ugo and Valerio that always supported me during these months. I wish to particularly thank five of my closest friends among the others. Carmine, who is my friend since we were 3 years old helped me in so many ways during these years, together with his family, and with so much patience that he is like a brother to me (Cosimo, Sara, Mattia and Alessio I will not forget you and I hope nothing but the best for you). Carlo, who despite his occupations never forgets to give me a call or to ask me how I feel, even if he notices a slight change of my mood (with him comes an army of other friends: Elvira, Giuseppe, Giulio, Orlando and Maria Virginia); Andrea, who is not my psychologist, but really helps in easing my mind,

which is one of the most amazing stuff a person could do for a guy who thinks too much even on small things like me; Manuela and her family (Filomena and Giovanni) who helped me throughout all my Milan days and not only, making me feel accepted and giving me some great memories; Gianmarco who is not only able to calm me down, but is also a great person to talk to.

If anyone of you is reading that right now I would you to know that I will be very happy to share with you a cup of coffee and a chat at any time, thus let us keep in touch so that I could thank you more in the future: you will not be forgotten.

# List of publications

Licciardo, G.D., Cappetta, C., Di Benedetto, L., Rubino, A., "Design of an offset-tolerant voltage sense amplifier bit-line sensing circuit for SRAM memories", *Electronics Letters*, 2016.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., Vigliar, M., "Weighted Partitioning for Fast Multiplierless Multiple-Constant Convolution Circuit", *IEEE Transactions on Circuits and Systems II: Express Briefs*, 2017.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., "FPGA optimization of convolution-based 2D filtering processor for image processing", 2016 8th Computer Science and Electronic Engineering Conference, CEEC 2016 - Conference Proceedings, 2017.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., "Design and FPGA implementation of a real-time processor for the HDR conversion of images and videos", 2016 8th Computer Science and Electronic Engineering Conference, CEEC 2016 - Conference Proceedings, 2017.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., "Application specific image processor for the extension of the dynamic range of images with multiple resolutions", 2016 IEEE International Conference on Electronics, Circuits and Systems, ICECS 2016, 2017.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., "Design of a Convolutional Two-Dimensional Filter in FPGA for Image Processing Applications", *Computers*, 2017.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., "Dynamic range enhancement for medical image processing", *Proceedings - 2017 7th International Workshop on Advances in Sensors and Interfaces, IWASI 2017*, 2017.

Cappetta, C., Licciardo, G.D., Di Benedetto, L., "Optimal design of a Gabor filter for medical imaging applications", *Proceedings - 2017 7th International Workshop on Advances in Sensors and Interfaces, IWASI 2017*, 2017.

Cappetta, C., Licciardo, G.D., Di Benedetto, L., "An FPGA oprimization of a multiple resolution architecture for LDR to HDR image conversion", ISSCS 2017 - International Symposium on Signals, Circuits and Systems, 2017.

Cappetta, C., Licciardo, G.D., Di Benedetto, L., "Hardware accelerator using Gabor filters for image recognition applications", *ISSCS 2017 - International Symposium on Signals, Circuits and Systems*, 2017.

Cappetta, C., Licciardo, G.D., Di Benedetto, L., "Hardware architecture for 2D Gaussian filtering of HD images on resource constrained platforms", ISSCS 2017 - International Symposium on Signals, Circuits and Systems, 2017.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., Rubino, A., Liguori, R., "Multiplier-Less Stream Processor for 2D Filtering in Visual Search Applications", *IEEE Transactions on Circuits and Systems for Video Technology*, 2018.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., "Design of a Gabor Filter HW Accelerator for Applications in Medical Imaging", *IEEE Transactions on Components, Packaging and Manufacturing Technology*, 2018.

Licciardo, G.D., Cappetta, C., Di Benedetto, L., "Design Criteria for Real-time Processing of HW Gabor Filters in Visual Search", 2018 IEEE International Symposium on Circuits and Systems (ISCAS), 2018.

# Summary

# **Contents**

| List of publications                                     | I    |

|----------------------------------------------------------|------|

| Figures Index                                            |      |

| Tables Index                                             |      |

| Abstract                                                 |      |

| Introduction                                             |      |

| i.1 Background                                           |      |

| i.2 Sampling, Quantization and Resolution                | XII  |

| i.3 Image Enhancement                                    | XIV  |

| i.3.1 Spatial Domain Techniques                          | XV   |

| i.3.1.1 Sharpening Filters                               | XVII |

| i.3.1 Frequency Domain Techniques                        |      |

| Chapter I. Bachet's Multipliers                          |      |

| I.1 Introduction                                         | 1    |

| I.2 Mathematical Background                              | 2    |

| I.3 Architectural Design                                 | 6    |

| I.3.1 Bachet's Multipliers                               | 6    |

| I.3.2 1D Filtering with Bachet MAC Units                 | 10   |

| I.3.3 2D Filtering with Bachet MAC Units                 | 13   |

| I.3.4 Memory Reduced Bachet's Multipliers                | 19   |

| I.4 Conclusions                                          |      |

| Chapter II. LDR2HDR Filters HW Design                    | 22   |

| II.1 Introduction                                        | 22   |

| II.1.1 Color Spaces and Encodings                        | 24   |

| II.1.1.1 RGB Color Space                                 |      |

| II.1.1.2 Y'UV Encoding                                   | 26   |

| II.2 Algorithmic Considerations                          |      |

| II.3 Numerical Considerations                            | 29   |

| II.4 Architectural Considerations                        | 33   |

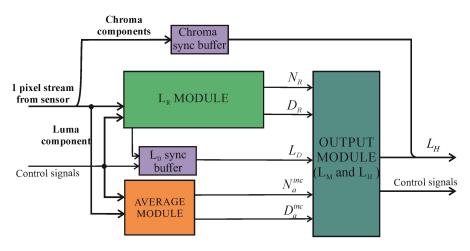

| II.4.1 L <sub>R</sub> and Output Modules                 | 35   |

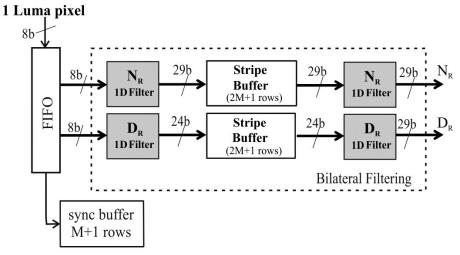

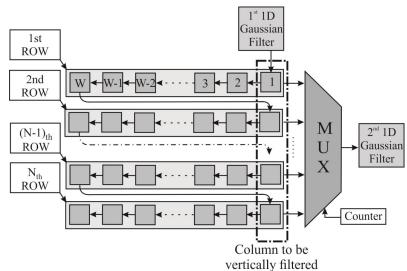

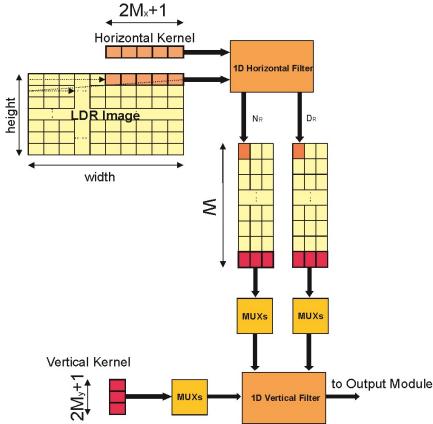

| II.4.2 Stripe Buffer and Multi-Resolution Implementation | 35   |

| II.5 Implementation Results                              | 37   |

| II.6 Conclusions                                         |      |

| Chapter III. Voltage Sense Amplifiers circuits for SRAMs | 42   |

| III.1 Introduction                                       | 42   |

| II.2 Background                                          | 42   |

| III.2.1 SRAMs Overview                                   |      |

| III.2.2 DRAMs Overview                                   |      |

| III.3 Sense Amplifiers                                   | 45   |

| III.4 Offset Issues                                        | 46 |

|------------------------------------------------------------|----|

| III.5 Latch CMOS                                           | 47 |

| III.6 Offset Compensation Schemes                          |    |

| III.6.1 Offset Compensation Schemes                        | 50 |

| III.6.2 Offset Cancellation Schemes                        |    |

| III.7 Proposed Scheme                                      |    |

| III.8 Results                                              |    |

| III.9 Comparisons                                          |    |

| III.10 Conclusions                                         |    |

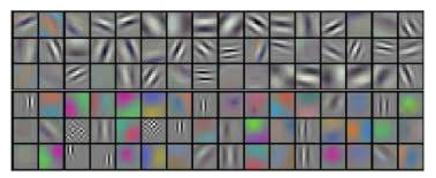

| Chapter IV. Gabor Filtering Applications for Visual Search | 59 |

| IV.1 Introduction                                          |    |

| IV.2 Theoretical Background                                |    |

| IV.3 Mathematical Remarks and Algorithmic Considerations   |    |

| IV.3.1 Filter Central Frequency, $f_0$                     |    |

| IV.3.2 Set of Orientations, $\theta$                       |    |

| IV.3.3 Gaussian Sharpness Values, γ and η                  |    |

| IV.3.4 Scales Dimensions, N <sub>s</sub>                   |    |

| IV.4 Numerical Remarks                                     |    |

| IV.5 Proposed Designs                                      |    |

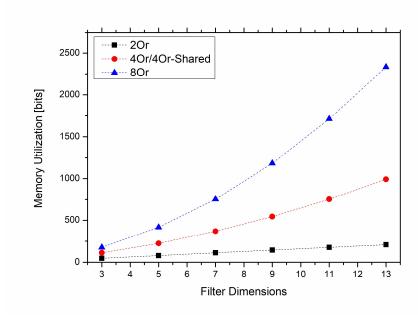

| IV.5.1 Gabor Coefficients Memories                         |    |

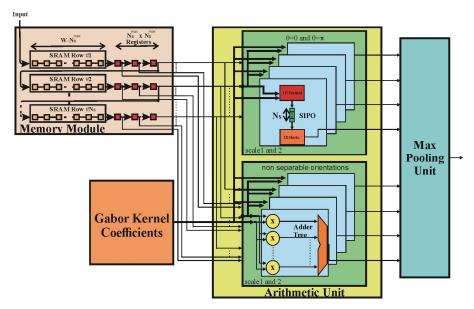

| IV.5.2 Memory Module                                       | 73 |

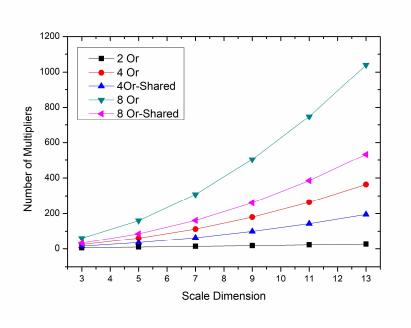

| IV.5.3 Arithmetic Unit                                     |    |

| IV.5.4 Control Unit                                        | 76 |

| IV.5.5 Max Pooling Unit                                    |    |

| IV.6 Synthesis and Results                                 |    |

| IV.7 Conclusions                                           |    |

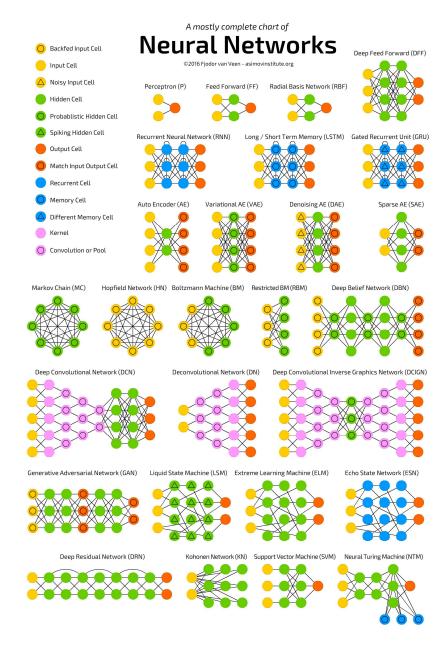

| Chapter V. Neural Networks in Multimedia Processing        |    |

| V.1 Introduction                                           |    |

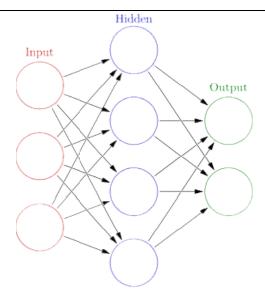

| V.2 Neural Networks                                        |    |

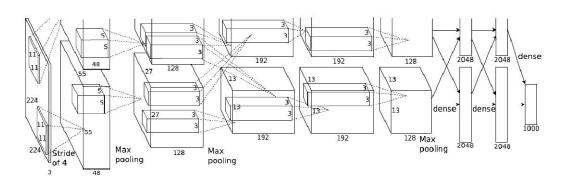

| V.2.1 AlexNet                                              |    |

| V.3 Chip Implementation for CNNs                           |    |

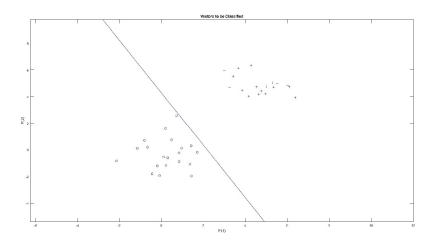

| V.4 Vector Quantization Theory                             |    |

| V.4.1 Scalar Quantization                                  | 93 |

| V.4.2 Vector Quantization                                  |    |

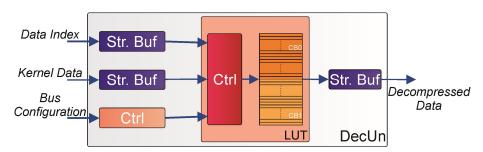

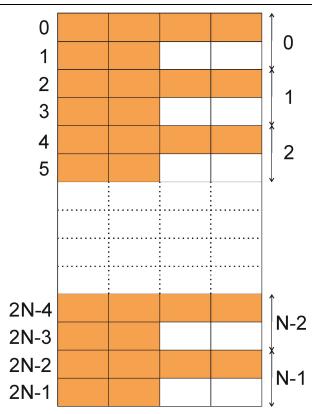

| V.5 Proposed HW Decompression Unit                         |    |

| V.6 Conclusions                                            |    |

| Chapter VI. Conclusions                                    |    |

| Bibliography                                               |    |

| Acronyms and Symbols List                                  |    |

# **Figures Index**

# Contents

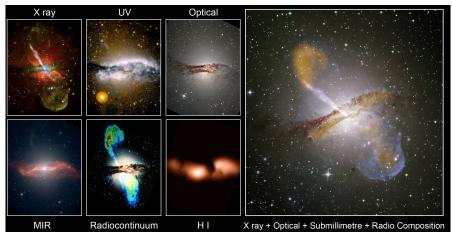

| Figure i.1 Image of galaxy Centaurus A at different wavelengths, together     |

|-------------------------------------------------------------------------------|

| with a composition of the same images                                         |

| Figure i.2 Principal applications in digital image processingXI               |

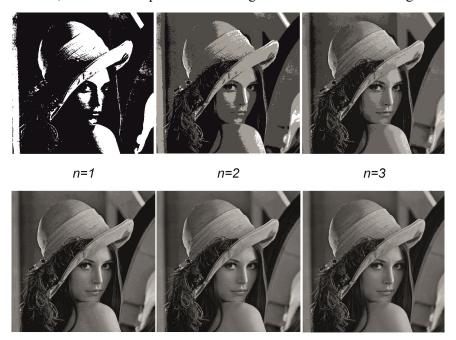

| Figure i.3 Lena grayscale image varying quantization levels, nXII             |

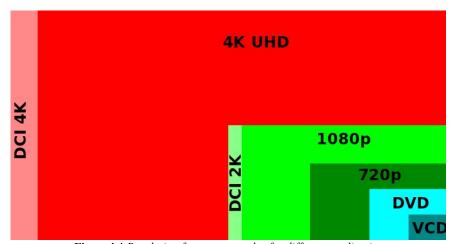

| Figure i.4 Resolution formats examples for different applicationsVIII         |

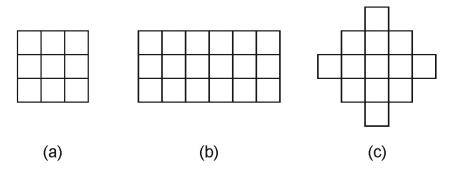

| Figure i.5 Examples of (a) square, (b) rectangular and (c) circular tile      |

| patterns in spatial domain image processing                                   |

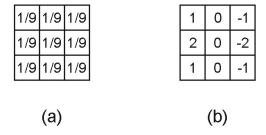

| Figure i.6 Examples of (a) average and (b) horizontal Sobel filtersXV         |

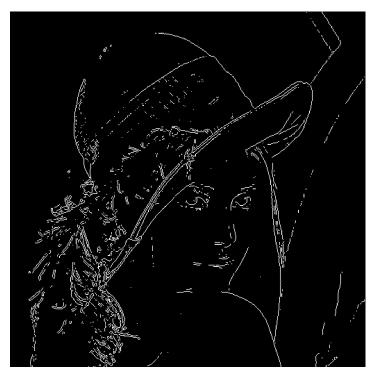

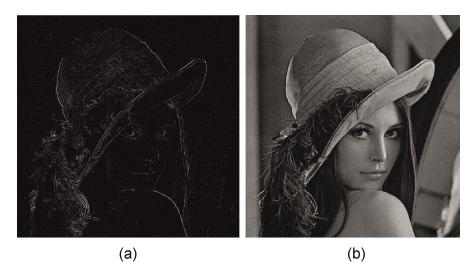

| Figure i.7 Examples of first derivative filtering using Sobel filtersXV       |

|                                                                               |

| Figure i.8 (a) Example of second derivative filtering using Laplacian filters |

| for detail enhancement and (b) sharpening of original Lena image XIV          |

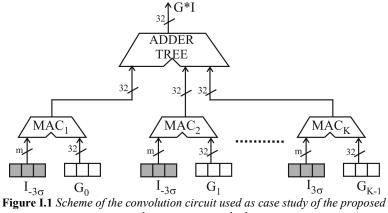

| Figure I.1 Scheme of the convolution circuit used as case study of the        |

| proposed decomposition method                                                 |

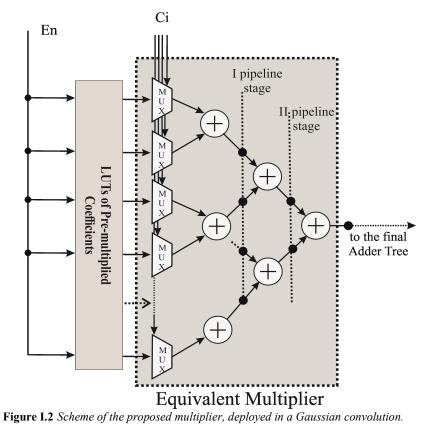

| Figure I.2 Scheme of the proposed multiplier, deployed in a Gaussian          |

| convolution                                                                   |

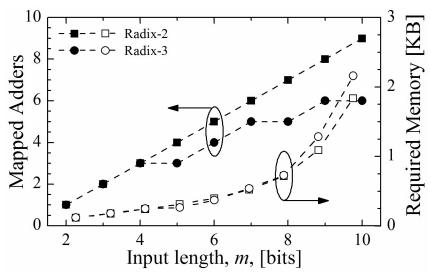

| Figure I.3 Comparison between required resources of the proposed              |

| partitioning method and the radix-2 DA for 1D filtering, with l=37 and        |

| $(3\sigma+1)=13$ ; the number of adders is given for a single multiplier      |

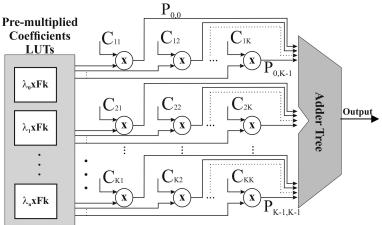

| Figure I.4 Scheme of the proposed 2D filter implementation using Bachet       |

| multipliers units                                                             |

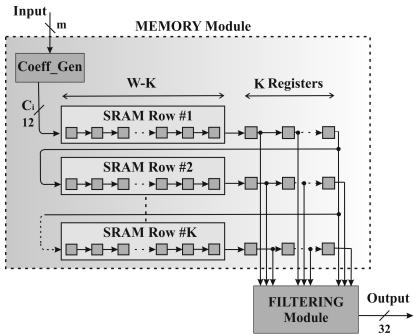

| Figure I.5 Block diagram of Filtering Module, representing the way the        |

| "equivalent" multipliers are interconnected                                   |

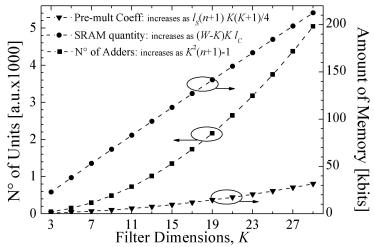

| Figure I.6 Required resources of the 2D convolution-based filter as a         |

| function of its dimensions, when m=8 bits and W=640 pixels                    |

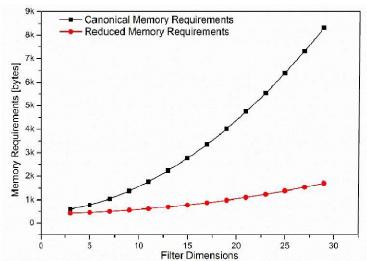

| Figure I.7 Required memory resources of the 2D convolution-based filter as    |

| a function of its dimensions, when m=8 bits                                   |

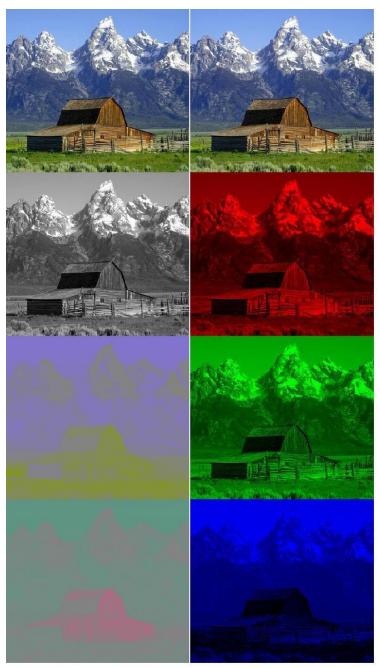

| Figure II.1 Y'UV and RGB components example                                   |

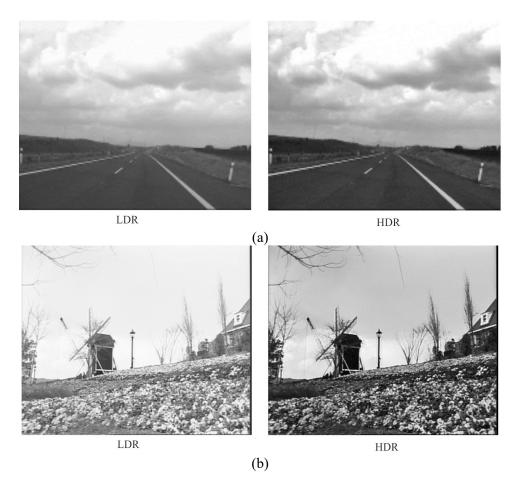

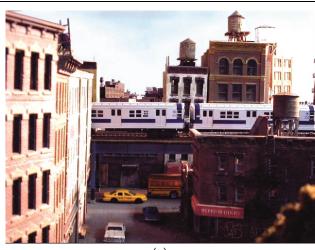

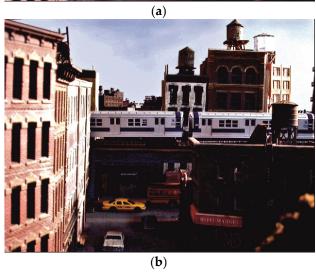

| Figure II.2 Application of the proposed expansion method to (a) "highway"     |

| (PSNR = 21.0 dB) and (b) "mill" (PSNR = 36.4 dB) frames                       |

| Figure II.3 General scheme of the proposed                                    |

| Figure II.4 Detailed scheme of the 1st stage, showing the sub-modules for     |

| the bilateral filtering calculation                                           |

| Figure II.5 Operation principle of the stripe-buffer                          |

| Figure II.6 Composition of the stripe-buffer with MUX structures for multi-   |

| resolution                                                                    |

| Figure II.7 Example of LDR to HDR conversion (a) the original LDR frame;      |

| (b) the HDR frame obtained through iTM                                        |

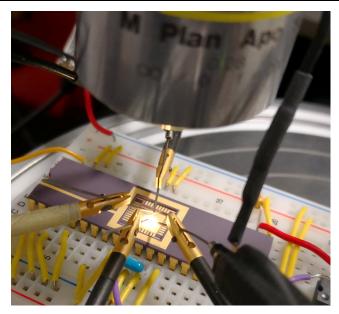

| Figure III.1 Breadboard measurement setup for the developed SRA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ١M |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| offset compensation design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43 |

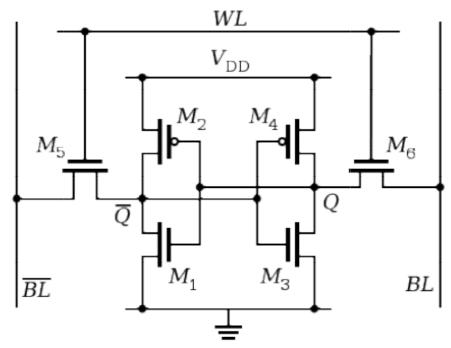

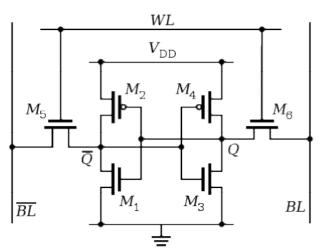

| Figure III.2 6T CMOS SRAM cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44 |

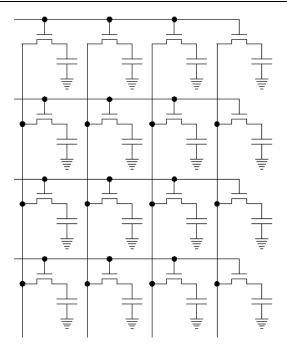

| Figure III.3 1T CMOS DRAM cell matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45 |

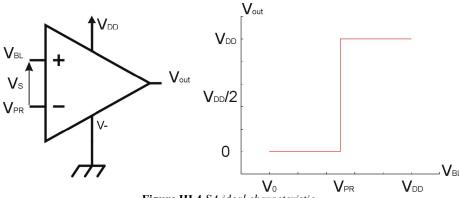

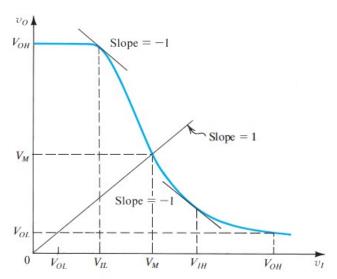

| Figure III.4 SA ideal characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46 |

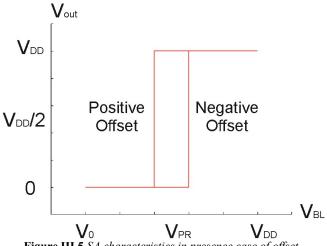

| Figure III.5 SA characteristics in presence case of offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 |

| Figure III.6 Scheme of a CMOS latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48 |

| Figure III.7 Ideal characteristic of a CMOS latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49 |

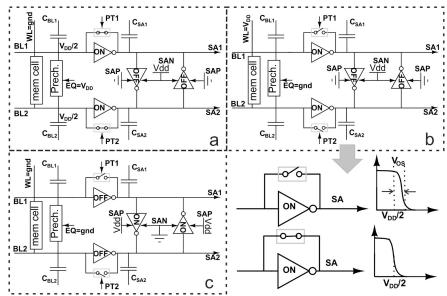

| Figure III.8 Scheme of the proposed circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52 |

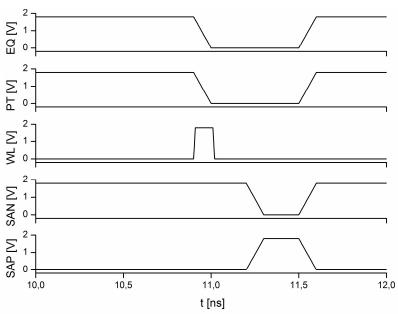

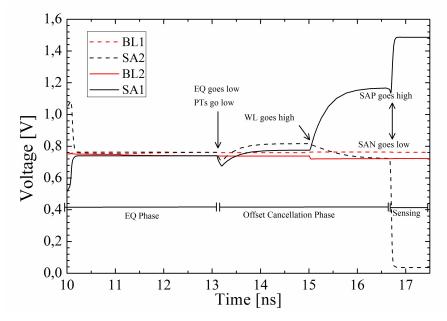

| Figure III.9 Waveform of the control signals over a single period of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53 |

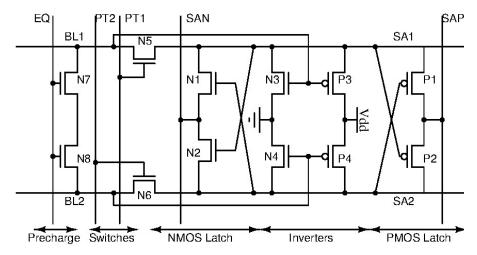

| Figure III.10 MOS implementation of the proposed sensing scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54 |

| Figure III.11 MOS BLs and SLs waveforms during the reading of a "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

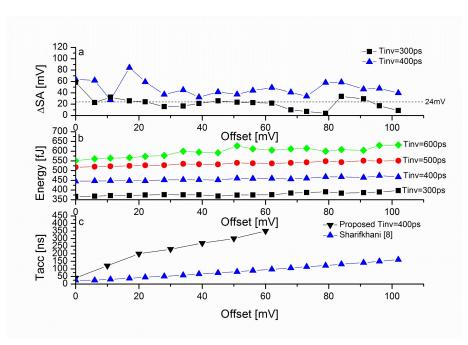

| Figure III.12 a) Sensed voltage varying VOS; b) Energy consumptions of the contract of the con |    |

| varying VOS; c) Minimum access times varying VOS at TINV=400ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| the proposed scheme and for the design in [M. Sharifkhani, E. Rahimine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| S.M. Jahinuzzaman, M. Sachdev, 2011]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

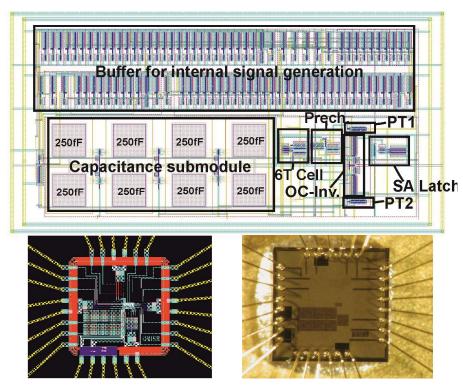

| Figure III.13 Design layout obtained using Virtuoso ADE and TSMC I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 180nm, overall layout showing also pins and wire bondings and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| obtained ASIC developed thanks to the Europractice mini@sic Prog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

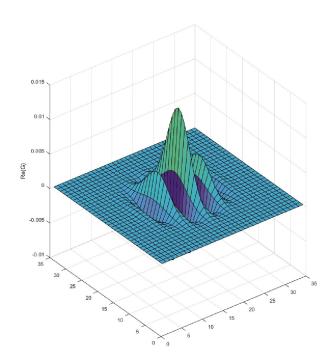

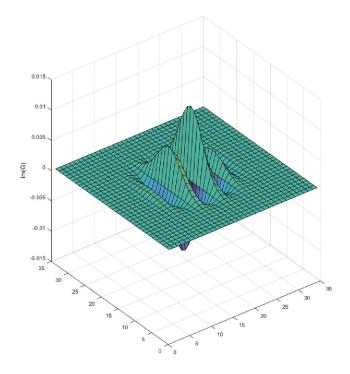

| Figure IV.1 Real part of Gabor filter with $f_0=0.2$ , $\theta=0$ , $\gamma=1$ and $\eta=1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61 |

| Figure IV.2 Imaginary part of Gabor filter with $f_0=0.2$ , $\theta=0$ , $\gamma=1$ and $\eta=1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

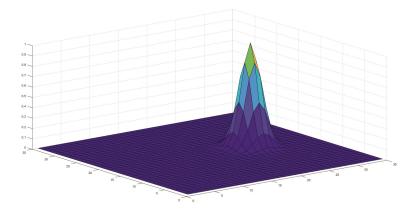

| Figure IV.3 FT of Gabor filter with $f_0=0.2$ , $\theta=0$ , $\gamma=1$ and $\eta=1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

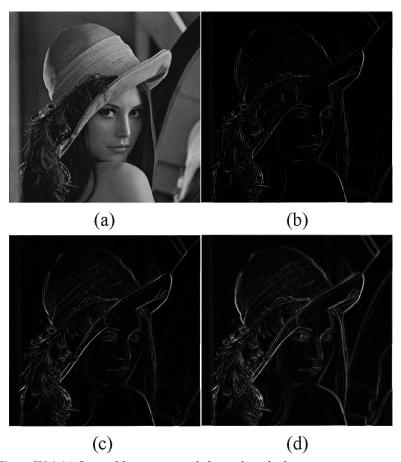

| Figure IV.4 (a) Original Lena image and obtained results for $f_0$ =0.2,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| $\eta=15$ , considering 7x7 Gabor filter and (b) two, (c) four and (d) e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| orientations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

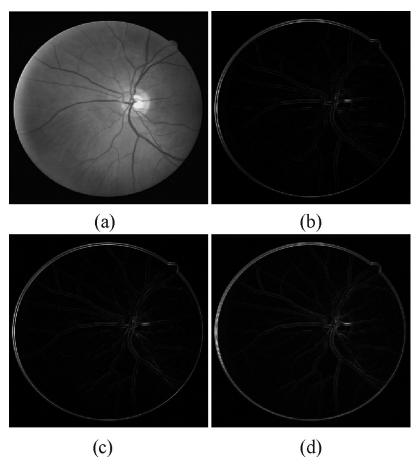

| Figure IV.5 (a) Original DRIVE dataset image and obtained results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| f0=0.2, $\gamma$ =1, $\eta$ =15, considering 7x7 Gabor filter and (b) two, (c) four and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

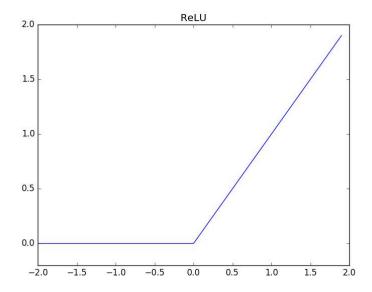

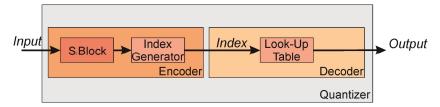

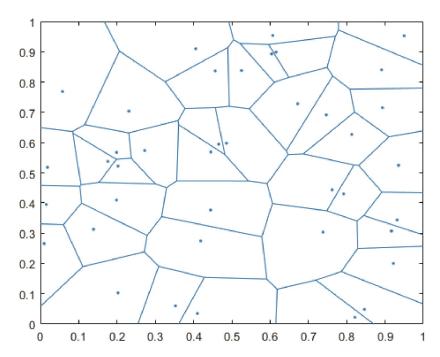

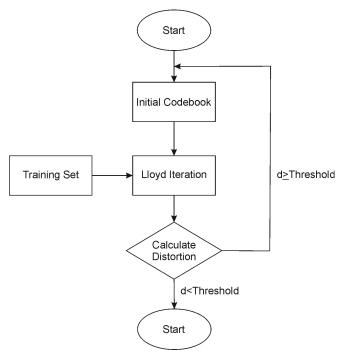

| eight orientations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |